# USER'S MANUAL

16-CHANNEL FORM A SWITCH M-MODULE

> MODEL M218

(FORMERLY HP E2270A)

Document Part No: 11029534

#### **COPYRIGHT**

C&H Technologies, Inc. (C&H) provides this manual "as is" without warranty of any kind, either expressed or implied, including but not limited to the implied warranties of merchantability and fitness for a particular purpose. C&H may make improvements and/or changes in the product(s) and/or program(s) described in this manual at any time and without notice.

This publication could contain technical inaccuracies or typographical errors. Changes are periodically made to the information herein; these changes will be incorporated in new editions of this publication.

## Copyright © 2006 by C&H Technologies, Inc.

Portions of this manual have been copied from relevant Hewlett-Packard (Agilent) User Manual's with their expressed written permission. The information and/or drawings set forth in this document and all rights in and to inventions disclosed herein which might be granted thereon disclosing or employing the materials, methods, techniques, or apparatus described herein, are the exclusive property of C&H Technologies, Inc.

A Reader's Comment Form is provided at the back of this publication. If this form has been removed address comments to:

C&H Technologies, Inc. Technical Publications 445 Round Rock West Drive Austin, Texas 78681-5012

Or visit our web site for support information at:

http://www.chtech.com.

C&H may use or distribute any of the information you supply in any way that it believes appropriate without incurring any obligations.

# AMENDMENT NOTICE

C&H Technologies, Inc. makes every attempt to provide up-to-date manuals with the associated equipment. Occasionally, changes are made to the equipment wherein it is necessary to provide amendments to the manual. If any amendments are provided for this manual they are printed on colored paper and will be provided with the module and manual. Manual updates may also be found on out web site at www.chtech.com.

### **NOTE**

The contents of any amendment may affect operation, maintenance, or calibration of the equipment.

#### INTRODUCTION

This manual describes the operation and use of the C&H Model M218 16-Channel Form A Switch M-Module (Part Number 11029530). This module was formerly manufactured by HP (Agilent) as Model E2270A. C&H obtained the manufacturing rights from Agilent and now manufacturers it as C&H Model M218. This mezzanine module is designed to interface within any M/MA-Module carrier adhering to the ANSI/VITA 12-1996 M-Module specification. These carriers are available in many formats such as Ethernet, VME, VXI, PXI, cPCI, and the PC.

Contained within this manual are the physical and electrical specifications, installation and startup procedures, functional description, and configuration and programming guidelines to adequately use the product.

This manual is based on a low level register access, and is written in such a manner to provide understanding to the user based on this type of access. If a driver is provided, please refer to the driver documentation for instruction using the higher level interface provided by the driver.

# TABLE OF CONTENTS

| 1.0 | GENERAL DES   | SCRIPTION                           | 1   |

|-----|---------------|-------------------------------------|-----|

|     | 1.1 PURPOS    | E OF EQUIPMENT                      | 1   |

|     | 1.2 SPECIFIO  | CATIONS OF EQUIPMENT                | 1   |

|     | 1.2.1         | Key Features                        |     |

|     | 1.2.2         | Specifications                      | 2   |

|     | 1.2.3         | Mechanical                          | 3   |

|     | 1.2.4         | Bus Compliance                      | 3   |

|     | 1.2.5         | Applicable Documents                | 3   |

| 2.0 |               | N                                   |     |

|     | 2.1 UNPACK    | ING AND INSPECTION                  | 5   |

|     |               | NG PRECAUTIONS                      |     |

|     | 2.3 INSTALI   | ATION OF M/MA MODULES               | 5   |

|     | 2.4 PREPAR    | ATION FOR RESHIPMENT                | 6   |

| 3.0 | FUNCTIONAL    | DESCRIPTION                         | 7   |

|     | 3.1 OVERVI    | EW                                  | 7   |

|     | 3.1.1         | M-Module Interface                  | 7   |

|     | 3.1.2         | Module Control                      | 7   |

|     | 3.1.3         | ID EEPROM                           |     |

|     | 3.1.4         | Row and Column Drivers              | 8   |

|     | 3.1.5         | Driver Power Switch                 |     |

|     | 3.2 IDENTIF   | ICATION AND CONFIGURATION REGISTERS | 10  |

|     | 3.2.1         | I/O Registers                       |     |

|     | 3.2.2         | Module Identification               | 13  |

| 4.0 |               |                                     |     |

|     | 4.1 FIFO STI  | RUCTURE                             | 14  |

|     | 4.2 RELAY S   | SET/RESET                           | 14  |

|     | 4.3 MATRIX    | DRIVE TO CHANNEL MAPPINGS           | 15  |

|     | 4.4 INTERRU   | JPTS                                | 15  |

| ΔDI | PENDIX A. CON | NECTOR S                            | Δ_1 |

# LIST OF FIGURES

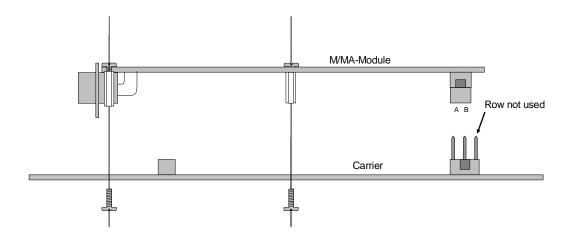

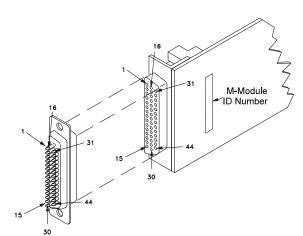

| Figure 1. M-MODULE Installation           | 5   |

|-------------------------------------------|-----|

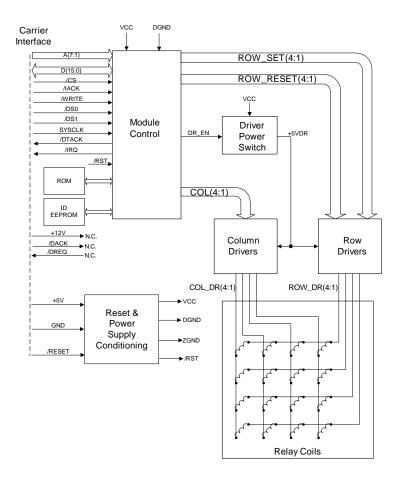

| Figure 2. M218 Functional Block Diagram   |     |

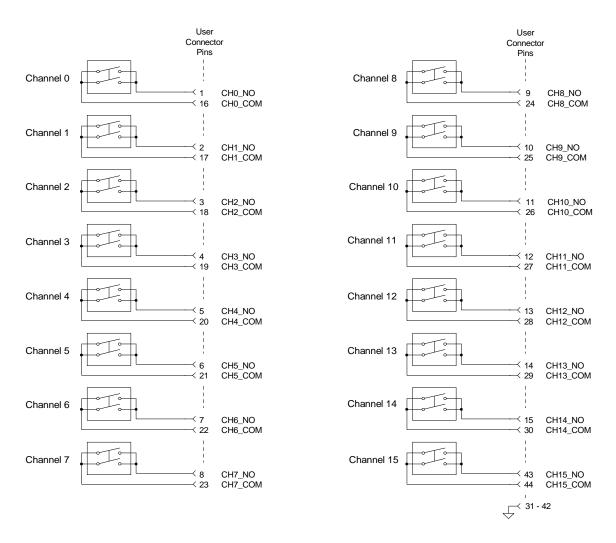

| Figure 3. M218 Switching Schematic        | 9   |

| Figure 4. M218 I/O Registers              | 11  |

| Figure A-1. Front Panel I/O Signals       | A-1 |

| LIST OF TABLES                            |     |

| Table I. Specifications                   | 2   |

| Table II. I/O Address Map/Command Summary |     |

| Table III. M/MA Module PROM IDENT Words   | 13  |

| Table IV. Matrix Drive.                   | 15  |

### 1.0 GENERAL DESCRIPTION

The M218 provides 16 one-wire switches on a single wide M-Module adhering to the ANSI/VITA 12-1996 specification for M-Modules. The M218 may be installed on any carrier board supporting the M-Module specification. Carriers are available that allow the M218 to be used in Ethernet, VXI, VME, PCI, cPCI and other system architectures.

# 1.1 PURPOSE OF EQUIPMENT

The M218 is a general purpose relay switch that can be used to connect test points on a device under test to instrumentation or to switch factory automation and fixturing.

**CAUTION:** This module uses latching relays that retain their last programmed state whenever power is removed (closed relays will remain closed until opened via your test program).

**CAUTION:** This module DOES NOT have provisions for on-board current limiting components (if input current can exceed 2A DC or 2A AC, you must install external current limiting circuitry)

### 1.2 SPECIFICATIONS OF EQUIPMENT

# 1.2.1 Key Features

- 16 Latching Relays

- Connector Type: 44-pin D-Sub

- Interrupts when requested relay movements have completed

- Latching relays retain last programmed state

- FIFO register structure allows fast system operation

- Single-width M-Module provide high-density and maximum flexibility of configuration

# 1.2.2 Specifications

The M218 incorporates the standard 40-pin, 20x2 row connector interfaces to the carrier board for power and data/control, but does not have the 24-pin optional connector for carrying user-connections back onto the carrier board.

The user input/output is provided through a standard 44-pin D-subminiature female receptacle. A mating connector kit can be ordered separately as AM111 (C&H Part Number 11029700-0001). CONEC part number 302A10889X (or equivalent) is used on the assembly. The connector pinouts are shown in Appendix A.

Table I. Specifications

#### **MAXIMUM RATINGS**

| Parameter               | Condition                            | Rating  | Units    |

|-------------------------|--------------------------------------|---------|----------|

| Voltage                 | Clean room Environment               | 200     | VDC      |

|                         | (any terminal to any other terminal) | 125     | VACrms   |

|                         |                                      | 175     | VAC peak |

|                         | Non-Clean room Environment           | 60      | VDC      |

|                         | (any terminal to any other terminal) | 48      | VACrms   |

|                         |                                      | 68      | VAC peak |

| Current (non-inductive) | Per Switch, DC                       | 2       | Α        |

|                         | Per Switch, AC                       | 2       | A peak   |

|                         | Per Module, DC                       | 8       | A        |

|                         | Per Module, AC                       | 8       | A peak   |

| Power                   | Per Switch, DC                       | 50      | W        |

|                         | Per Switch, AC                       | 50      | VA       |

|                         | Per Module, DC                       | 200     | W        |

|                         | Per Module, AC                       | 200     | VA       |

| Thermal Offset          |                                      | < 3 typ | μV       |

#### **RESISTANCE**

| Parameter      | Condition                     | Rating              | Units |

|----------------|-------------------------------|---------------------|-------|

| Closed Channel | Initial                       | < 0.2 typ           | Ω     |

|                | End of Life                   | < 2                 | Ω     |

| Insulation     | Between any two points        |                     |       |

|                | ≤40°C, ≤65% relative humidity | 10 <sup>8</sup> typ | Ω     |

|                | ≤25°C, ≤40% relative humidity | 10 <sup>8</sup> typ | Ω     |

#### **RELAYS**

| Parameter          | Condition                     | Rating              | Units      |

|--------------------|-------------------------------|---------------------|------------|

| Relay Life         | at rated load                 | 10 <sup>5</sup>     | operations |

| Time to open/close | register programming          | 8                   | ms         |

| Insulation         | Between any two points        | _                   |            |

|                    | ≤40°C, ≤65% relative humidity | 10 <sup>8</sup> typ | Ω          |

|                    | ≤25°C, ≤40% relative humidity | 10 <sup>8</sup> typ | Ω          |

### **AC CHARACTERISTICS**

| Parameter                      | Condition          | Rating   | Units |

|--------------------------------|--------------------|----------|-------|

| Typical Bandwidth              | -3dB               | > 10     | MHz   |

| Crosstalk (channel-to-channel) | <100 KHz           | -64 typ  | dB    |

|                                | <1 MHz             | -44 typ  | dB    |

|                                | <10 MHz            | -24 typ  | dB    |

| Closed Channel Capacitance     | Channel-to-Channel | < 15 typ | pF    |

|                                | Channel-to-Common  | < 25 typ | pF    |

#### 1.2.3 Mechanical

The mechanical dimensions of the module are in conformance with ANSI/VITA 12-1996 for single-wide M-Module modules. The nominal dimensions are 5.687" (144.5 mm) long  $\times$  2.082" (52.9 mm) wide.

# 1.2.4 Bus Compliance

The module complies with the ANSI/VITA 12-1996 Specification for single-wide M-Modules and the MA-Module trigger signal extension. The module also supports the optional IDENT and VXI-IDENT functions.

Module Type: M-Module

Addressing: A08 Data: D16

Interrupts: supported DMA: not supported Triggers: not supported

Identification: IDENT

Manufacturer ID: 0FFF<sub>16</sub> (See note below)

Model Number: 0686<sub>16</sub> VXI Model Number: 025B<sub>16</sub>

Note: C&H obtained the manufacturing rights from Hewlett Packard (Agilent) for this module. The ID's have been retained as Hewlett Packard to provide compatibility with existing SW drivers.

# 1.2.5 Applicable Documents

ANSI/VITA 12-1996 Standard for The Mezzanine Concept M-Module Specification, Approved May 20, 1997, American National Standards Institute and VMEbus International Trade Association, 7825 E. Gelding Dr. Suite 104, Scottsdale, AZ 85260-3415, http://www.vita.com

#### 2.0 INSTALLATION

#### 2.1 UNPACKING AND INSPECTION

Verify that there has been no damage to the shipping container. If damage exists then the container should be retained, as it will provide evidence of carrier caused problems. Such problems should be reported to the shipping courier immediately, as well as to C&H. If there is no damage to the shipping container, carefully remove the module from its box and anti static bag and inspect for any signs of physical damage. If damage exists, report immediately to C&H.

### 2.2 HANDLING PRECAUTIONS

The module contains components that are sensitive to electrostatic discharge. When handling the module for any reason, do so at a static-controlled workstation, whenever possible. At a minimum, avoid work areas that are potential static sources, such as carpeted areas. Avoid unnecessary contact with the components on the module.

### 2.3 INSTALLATION OF M/MA MODULES

All M-Modules must be installed into the carrier before the carrier is installed into the host system. To install a module, firmly press the connector on the M/MA-Module together with the connector on the carrier as shown in Figure 1. Secure the module through the holes in the bottom shield using the original screws.

CAUTION: M/MA-Module connectors are NOT keyed. Use extra caution to avoid misalignment. Applying power to a misaligned module can damage the M/MA-Module and carrier.

Figure 1. M-MODULE Installation

### 2.4 PREPARATION FOR RESHIPMENT

If the module is to be shipped separately it should be enclosed in a suitable water and vapor proof anti-static bag. Heat seal or tape the bag to insure a moisture-proof closure. When sealing the bag, keep trapped air volume to a minimum. The shipping container should be a rigid box of sufficient size and strength to protect the equipment from damage. If the module was received separately from a C&H system, then the original module shipping container and packing material may be re-used if it is still in good condition.

### 3.0 FUNCTIONAL DESCRIPTION

### 3.1 OVERVIEW

A simplified functional block diagram is shown in Figure 2.

Figure 2. M218 Functional Block Diagram

#### 3.1.1 M-Module Interface

The M-Module Interface allows communication between the M218 and the carrier module. The interface is an asynchronous 16-bit data bus with interrupt capabilities. The interface adheres to the ANSI/VITA 12-1996 Standard for The Mezzanine Concept M-Module Specification for MA modules.

### 3.1.2 Module Control

This block contains all of the logic for the module including all registers, interrupt control and carrier interface.

#### 3.1.3 ID EEPROM

The EEPROM holds sixty-four 16-bit words of M-Module ID data and VXI M-Module data. Refer to "ID EEPROM Register" on page 10 for EEPROM contents.

#### 3.1.4 Row and Column Drivers

The module uses a matrix drive scheme (rows and columns) in which a maximum of four of the relays (one row) can be operated at any one time. An on-board timer (part of Module Control block) ensures the relay coils have been driven long enough for the contacts to move and settle.

The Row Driver block translates the ROW\_SET(4:1) and ROW\_RESET(4:1) command lines from the Module Control block into bipolar and tri-state capable buffered drive signals. The ROW\_DR(4:1) signals provide either current source from the +5VDR supply (relay set), current sink to ground (relay reset), or tri-stated output (both current-source and current-sink off). Each output is tri-stated whenever that particular row is not being driven.

The Column Driver block translates the COL(4:1) command lines from Module Control into the bipolar buffered drive signals, COL\_DR(4:1). The COL\_DR(4:1) signals provide either current source from the +5VDR supply (relay reset) or current sink to ground (relay set).

#### 3.1.5 Driver Power Switch

This block removes all power from the Row and Column Driver circuitry except when needed to move relays. This FET switch is open at power-up to prevent any relay contact movement until register writes cause drive-power to be applied.

# 3.1.7 Relay Coils

This block contains the 16 relay coils arranged as a 4x4 matrix. To close a relay, a ROW\_DR line sources current while a COL\_DR line sinks current to ground. To open a relay, a COL\_DR line sources current while a ROW\_DR line sinks current to ground. Refer to Figure 3 for switching schematic.

### 3.1.8 Reset and Power Conditioning

This block filters +5V power to produce VCC power (+5V) for logic and isolates the various grounds used by the module. This block also processes the /RESET signal from the Carrier Interface and monitors power to produce the /RST reset signal for the module.

Figure 3. M218 Switching Schematic

# 3.2 IDENTIFICATION AND CONFIGURATION REGISTERS

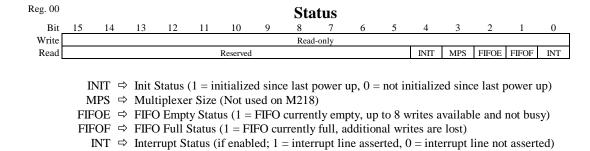

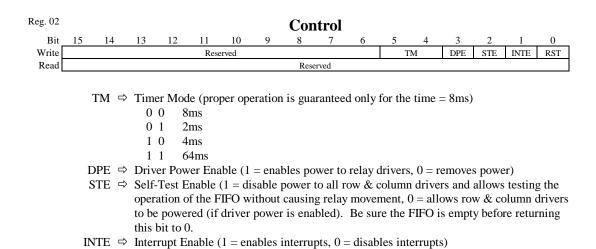

# 3.2.1 I/O Registers

There are a variety of registers used to configure and control the module. These registers are located in the IOSpace. The address map of the registers is shown in Table II. Details of the registers are provided in Figure 4.

Table II. I/O Address Map/Command Summary

|           | Register Name        | Register Type | FIFO-able<br>Register<br>(Y/N) |

|-----------|----------------------|---------------|--------------------------------|

| 00h       | Status Register      | Read Only     | N                              |

| 02h       | Control Register     | Read/Write    | N                              |

| 04h-0Eh   | Reserved             | NA            | N                              |

| 10h       | Row 0 Set Register   | Read/Write    | Y                              |

| 12h       | Row 0 Reset Register | Read/Write    | Y                              |

| 14h       | Row 1 Set Register   | Read/Write    | Y                              |

| 16h       | Row 1 Reset Register | Read/Write    | Y                              |

| 18h       | Row 2 Set Register   | Read/Write    | Y                              |

| 1Ah       | Row 2 Reset Register | Read/Write    | Y                              |

| 1Ch       | Row 3 Set Register   | Read/Write    | Y                              |

| 1Eh       | Row 3 Reset Register | Read/Write    | Y                              |

| 20h - 7Eh | Unused               | NA            | N                              |

| 80h - FEh | ID EEPROM            | Read/Write    | N                              |

RST  $\Rightarrow$  Reset (1 = initiates a soft reset, 0 = releases module from reset condition)

Figure 4. M218 I/O Registers

| Reg. 10      |    |          |       |            |        | 1          | Row              | 0 Set    | Reg        | gister |     |   |           |           |           |           |

|--------------|----|----------|-------|------------|--------|------------|------------------|----------|------------|--------|-----|---|-----------|-----------|-----------|-----------|

| Bit          | 15 | 14       | 13    | 12         | 11     | 10         | 9                | 8        | 7          | 6      | 5   | 4 | 3         | 2         | 1         | 0         |

| Write        |    |          |       |            |        | Unus       | sed              |          |            |        |     |   | R0C3      | R0C2      | R0C1      | R0C0      |

| Read         |    |          |       |            |        | Unus       | sed              |          |            |        |     |   | R0C3      | R0C2      | R0C1      | R0C0      |

| _            |    |          |       |            |        |            |                  |          |            |        |     |   |           |           |           |           |

| Reg. 12      |    |          |       |            |        | R          | ow 0             | Res      | et Re      | egiste | r   |   |           |           |           |           |

| Bit          | 15 | 14       | 13    | 12         | 11     | 10         | 9                | 8        | 7          | 6      | 5   | 4 | 3         | 2         | 1         | 0         |

| Write        |    |          |       |            |        | Unu        | sed              |          |            |        |     |   | R0C3      | R0C2      | R0C1      | R0C0      |

| Read         |    |          |       |            |        | Unus       | sed              |          |            |        |     |   | R0C3      | R0C2      | R0C1      | R0C0      |

| _            |    |          |       |            |        |            |                  |          |            |        |     |   |           |           |           |           |

| Reg. 14      |    |          |       |            |        | 1          | Row              | 1 Set    | Reg        | gister |     |   |           |           |           |           |

| Bit          | 15 | 14       | 13    | 12         | 11     | 10         | 9                | 8        | 7          | 6      | 5   | 4 | 3         | 2         | 1         | 0         |

| Write        |    |          |       |            |        | Unus       | sed              |          |            |        |     |   | R1C3      | R1C2      | R1C1      | R1C0      |

| Read         |    |          |       |            |        | Unu        | sed              |          |            |        |     |   | R1C3      | R1C2      | R1C1      | R1C0      |

| _            |    |          |       |            |        |            |                  |          |            |        |     |   |           |           |           |           |

| Reg. 16      |    |          |       |            |        | D          | ATT 1            | Dog      | of D       | ariata | 14  |   |           |           |           |           |

| Bit          | 15 | 14       | 13    | 12         | 11     | 10         | <b>UW 1</b><br>9 | 8 Nes    | ei Ni<br>7 | egiste | T 5 | 4 | 3         | 2         | 1         | 0         |

| Write        | 13 | 14       | 13    | 12         | 11     | Unus       |                  |          |            | 0      | 3   | 4 | R1C3      | R1C2      | R1C1      | R1C0      |

| Read         |    |          |       |            |        | Unus       |                  |          |            |        |     |   | R1C3      | R1C2      | R1C1      | R1C0      |

| Read         |    |          |       |            |        | Cita       | 3CU              |          |            |        |     |   | Ries      | RICZ      | KICI      | RICO      |

| Dog 19       |    |          |       |            |        | _          | _                | • ~      | _          |        |     |   |           |           |           |           |

| Reg. 18      |    |          |       |            |        | J          |                  |          | •          | gister |     |   |           |           |           |           |

| Bit          | 15 | 14       | 13    | 12         | 11     | 10         | 9                | 8        | 7          | 6      | 5   | 4 | 3         | 2         | 1         | 0         |

| Write        |    |          |       |            |        | Unus       |                  |          |            |        |     |   | R2C3      | R2C2      | R2C1      | R2C0      |

| Read         |    |          |       |            |        | Unus       | sed              |          |            |        |     |   | R2C3      | R2C2      | R2C1      | R2C0      |

|              |    |          |       |            |        |            |                  |          |            |        |     |   |           |           |           |           |

| Reg. 1A      |    |          |       |            |        | R          | ow 2             | Res      | et Re      | egiste | r   |   |           |           |           |           |

| Bit          | 15 | 14       | 13    | 12         | 11     | 10         | 9                | 8        | 7          | 6      | 5   | 4 | 3         | 2         | 1         | 0         |

| Write        |    |          |       |            |        | Unus       | sed              |          |            |        |     |   | R2C3      | R2C2      | R2C1      | R2C0      |

| Read         |    |          |       |            |        | Unus       | sed              |          |            |        |     |   | R2C3      | R2C2      | R2C1      | R2C0      |

| _            |    |          |       |            |        |            |                  |          |            |        |     |   |           |           |           |           |

| Reg. 1C      |    |          |       |            |        | 1          | Row              | 3 Set    | Reg        | gister |     |   |           |           |           |           |

| Bit          | 15 | 14       | 13    | 12         | 11     | 10         | 9                | 8        | 7          |        | 5   | 4 | 3         | 2         | 1         | 0         |

| Write        |    |          |       |            |        | Unus       | sed              |          |            |        |     |   | R3C3      | R3C2      | R3C1      | R3C0      |

| Read         |    |          |       |            |        | Unus       | sed              |          |            |        |     |   | R3C3      | R3C2      | R3C1      | R3C0      |

| _            |    |          |       |            |        |            |                  |          |            |        |     |   |           |           | ı         |           |

| Reg. 1E      |    |          |       |            |        | ъ          | 1                | D        | .4 D.      | •_4_   |     |   |           |           |           |           |

|              |    |          |       |            |        |            |                  |          |            | egiste |     |   | 2         | •         |           |           |

| Bit<br>Write | 15 | 14       | 13    | 12         | 11     | 10<br>Unus | 9                | 8        | 7          | 6      | 5   | 4 | 3<br>D2C2 | 2<br>D2C2 | 1<br>D2C1 | 0<br>P2C0 |

| _            |    |          |       |            |        |            |                  |          |            |        |     |   | R3C3      | R3C2      | R3C1      | R3C0      |

| Read         | ъ  | <u> </u> | . D   | <i>a</i> 1 |        | Unus       |                  | 1. 0     |            | 1 . \  |     |   | R3C3      | R3C2      | R3C1      | R3C0      |

|              | R: | KUV 5    | > K∩W | x Col      | iimn v | (1 = c1)   | ose re           | 1av () = | = onen     | relay) |     |   |           |           |           |           |

RxCy  $\Rightarrow$  Row x, Column y (1 = close relay, 0 = open relay)

Note: The Switch M-Modules use a row and column relay drive scheme. To close a particular relay, write a logic "1" to the corresponding column in a Row n Set register. To open a relay, write a logic "0" in the corresponding column in a Row n Reset register. For example, to close the Channel 04 relay on the M218 (Row 1, Column 0 in relay drive scheme) place a logic "1" in bit 00 of the Row 1 Set register. To open this relay, place a logic "0" in bit 00 of the Row 1 Reset register. Table V shows the correlation of the matrix drive rows and columns to Switch M-Module channels.

Figure 4. M218 I/O Registers (continued)

#### 3.2.2 Module Identification

The M218 supports the identification function called IDENT. This IDENT function provides information about the module and is stored in a sixteen-word deep (32 byte) serial PROM. Access is accomplished with read/write operations on the last address in IOSpace (hex FE) and the data is read one bit at a time. The PROM is compatible with a standard IC 9603 type PROM. For specific timing information refer to the 9603 or compatible PROM data sheet. Data should not be written to the PROM.

The module also supports the VXI-IDENT function. This function is <u>not</u> part of the approved ANSI/VITA 12-1996 standard. This extension to the M-module IDENT function increases the size of the PROM to 64 words and includes VXI compatible ID and Device Type Registers. Details are shown in Table III.

Word Description Value (hex) 0 Sync Code 5346 1 Module Number 0686 2 **Revision Number** 0001 3 Module Characteristics <sup>2</sup> 0868 4-7 Reserved 0000 8-15 M-Module Specific 0000 16 VXI Sync Code **ACBA** 0FFF<sup>3</sup> VXI ID 17 VXI Device Type 18 F25B (M218) 19-31 Reserved 0000

Table III. M/MA Module PROM IDENT Words

#### Notes:

32-63

The Revision Number is the functional revision level of the module. It does not necessarily correspond

to the hardware assembly level.

0000

2) The Module Characteristics bit definitions are:

M-Module Specific

| Bit(s) | <u>Description</u>          |

|--------|-----------------------------|

| 15     | 0 = no burst access         |

| 14/13  | unused                      |

| 12     | $0 = does not need \pm 12V$ |

| 11     | 1 = needs + 5V              |

| 10     | 0 = no trigger outputs      |

| 9      | 0 = no trigger inputs       |

| 8/7    | 00 = no DMA requestor       |

| 6/5    | 11 = interrupt type         |

| 4/3    | 01 = 16-bit data            |

| 2/1    | 00 = 8-bit address          |

| 0      | 0 = no memory access        |

- 3) The VXI ID of 0xFFF is the identification value for Hewlett-Packard. C&H has left the ID equal to this value to allow operation with existing E2270A software drivers. The revision number (see note 1) can be used to identify the module as manufactured by C&H.

- 4) The VXI Device Type word contains the following information:

Bit(s) Description

$F_{16} = 256$  bytes of required memory

11-0  $260_{16} = C\&H$  specified VXI model code for M218

#### 4.0 OPERATION

The M218 is a register-based instrument that is controlled through a series of I/O registers described in Section 3.2.1. The exact method of accessing and addressing the I/O registers is dependent on the M-Module carrier used to interface the module to your data acquisition or test system. Refer to the carrier's documentation for information on the address mapping of an M-Module's I/O registers and to your system software documentation for details on data access.

Typically a high level driver is available to aid in control of the module. Refer to the software driver documentation for instructions on using the driver.

#### 4.1 FIFO STRUCTURE

The FIFO (First-In-First-Out) structure allows multiple writes to the module to be stacked-up. This helps reduce interrupt overhead by allowing an interrupt only after the completion of the last relay operation in a sequence of up to eight operations. Eight was chosen because it allows at least one *open* and one *close* to each of the four relay rows, allowing a complete change of all relay states.

If the M-Module is enabled to interrupt, it asserts the INT line on the M-Module interface to the Carrier when the last commanded relay operation in the FIFO has completed. For example, if relays in only one row were instructed to move, the module asserts an interrupt after that one row has been driven. If four rows were instructed to move (four writes to the FIFO--see note below), then the module asserts an interrupt only after the completion of the fourth operation.

Note: The module asserts an interrupt after the relay drive time is complete (relay drive timer) and no other operations have been stored in FIFO. The above example assumes the four writes are stored in FIFO one after the other with very little time between the writes. If, in the above example, the amount of time between writes is greater than the relay drive time (8 ms), the module would actually interrupt four times--one interrupt after driving each relay.

## 4.2 RELAY SET/RESET

When the FIFO is empty (no relay operations pending) bits 03, 02, 01, and 00 in the above registers indicate the state of the corresponding relay. Logic "1" means the relay in Row n Column n is closed or soon will be (depending on the FIFO Empty Status bit's state). Logic "0" means the corresponding relay is open. Following are some general notes on relay operation:

- 1. Writing to a Row n Set register closes the relays only in the bit positions set to logic "1." Writing logic "0" to a Row n Set register has no effect on relay position. Writing to a Row n Reset register opens relays only for the bit positions set to logic "0." Writing logic "1" to a Row n Reset register has no effect on relay position.

- 2. Reading either the **Row n Set** or **Row n Reset** register addresses returns identical data because they are actually mapped to the same register. When you write to one of these registers (and FIFO is not full), the data is stored in the register and stored in FIFO.

- 3. The Row n Set/Reset readback registers return the programmed relay state only if you use the module correctly. Since the driver power can be disabled (the power-on state), the **Row n Set** and **Row n Reset** registers can be written to and read from without moving any relay contacts.

- 4. When the module loses power, any closed relays remain closed (latching relays). When power is restored, the relays remain closed but the Row n Set and Row n Reset registers have lost their relay state information. This relay information is lost whenever power is cycled or the carrier asserts /RESET. You must initialize the module after a power-up or /RESET to achieve correlation between the Row n Set/Reset readback registers and the actual relay positions. To initialize the module:

- a. Enable driver power.

- b. Write all four column bits to zero in each Row n Reset register.

You can check for initialization by reading the Init Status bit. If the module has not been initialized since the last power-up or /RESET, the Init Status bit will be logic "0". The Init Status bit is set to logic "1" whenever the module has been successfully initialized.

- 1. To guarantee break-before-make relay operation, write to the Row n Reset registers before writing to the Row n Set registers.

- 2. It is important to use the FIFO status bits when writing to the Row n Set/Reset registers, especially when writing in bursts (such as when resetting the module's relays). Writing to a Row n Set/Reset register when the FIFO is full results in the loss of data since the FIFO has no room to hold it. You should always check the FIFO FULL status to ensure that FIFO is not full before writing to a Row n Set/Reset register.

# 4.3 MATRIX DRIVE TO CHANNEL MAPPINGS

Table IV correlates the matrix drive rows and columns to channel numbers on the M218.

Column 0 Column 1 Column 2 Column 3 **Matrix Drive** Channel 0 Channel 1 Channel 2 Channel 3 Row 0 Channel 4 Channel 5 Channel 6 Channel 7 Row 1 Channel 8 Channel 9 Channel 10 Channel 11 Row 2 Row 3 Channel 12 Channel 13 Channel 14 Channel 15

Table IV. Matrix Drive

# 4.4 INTERRUPTS

Module interrupts are enabled by setting the INTE bit in the Control register; however, routing of the m-module interrupt request to your system is dependent on the m-module carrier and the system interface. Refer to user manuals for those devices for details.

If the M-Module is enabled to interrupt, it asserts the INT line on the M-Module interface to the Carrier when the last commanded relay operation in the FIFO has completed. For example, if relays in only one row were instructed to move, the module asserts an interrupt after that one row has been driven. If four rows were instructed to move (four writes to the FIFO--see note below), then the module asserts an interrupt only after the completion of the fourth operation.

Note: The module asserts an interrupt after the relay drive time is complete (relay drive timer) and no other operations have been stored in FIFO. The above example assumes the four writes are stored in FIFO one after the other with very little time between the writes. If, in the above example, the amount of time between writes is greater than the relay drive time (8 ms), the module would actually interrupt four times--one interrupt after driving each relay.

### **APPENDIX A: CONNECTORS**

MAXIMUM VOLTAGE/CURRENT. The maximum voltage that may be applied to any connector on the M218, M219, or M220 is 200 VDC, 125 VAC rms, or 175 VAC peak--these limits apply only if the product is installed in a humidity-controlled (<60% RH) environment where airborne contaminants and transients are controlled, and there is NOT a relay connection made to power mains. If these conditions CANNOT be maintained, then the maximum voltage is 60 VDC, 48 VAC-rms or 68 VAC-peak.

The maximum current (non-inductive) that may be applied to the M218, M219, or M220 is:

Per Switch: 2 ADC, 2 AAC peak Per Module: 8 ADC, 8 AAC peak

| Pin # | Use     | Pin # | Use      | Pin# | Use      |

|-------|---------|-------|----------|------|----------|

| 1     | CH0_NO  | 16    | CH0_COM  | 31   | Chassis  |

| 2     | CH1_NO  | 17    | CH1_COM  | 32   | Chassis  |

| 3     | CH2_NO  | 18    | CH2_COM  | 33   | Chassis  |

| 4     | CH3_NO  | 19    | CH3_COM  | 34   | Chassis  |

| 5     | CH4_NO  | 20    | CH4_COM  | 35   | Chassis  |

| 6     | CH5_NO  | 21    | CH5_COM  | 36   | Chassis  |

| 7     | CH6_NO  | 22    | CH6_COM  | 37   | Chassis  |

| 8     | CH7_NO  | 23    | CH7_COM  | 38   | Chassis  |

| 9     | CH8_NO  | 24    | CH8_COM  | 39   | Chassis  |

| 10    | CH9_NO  | 25    | CH9_COM  | 40   | Chassis  |

| 11    | CH10_NO | 26    | CH10_COM | 41   | Chassis  |

| 12    | CH11_NO | 27    | CH11_COM | 42   | Chassis  |

| 13    | CH12_NO | 28    | CH12_COM | 43   | CH15_NO  |

| 14    | CH13_NO | 29    | CH13_COM | 44   | CH15_COM |

| 15    | CH14_NO | 30    | CH14_COM |      |          |

Figure A-1. Front Panel I/O Signals

# NOTES:

### READER'S COMMENT FORM

Your comments assist us in improving the usefulness of C&H's publications; they are an important part of the inputs used for revision.

C&H Technologies, Inc. may use and distribute any of the information that you supply in any way that it believes to be appropriate without incurring any obligation whatsoever. You may, of course, continue to use the information, which you supply.

Please refrain from using this form for technical questions or for requests for additional publications; this will only delay the response. Instead, please direct your technical questions to your authorized C&H representative.

| COMMENTS: |  |  |  |

|-----------|--|--|--|

|           |  |  |  |

|           |  |  |  |

|           |  |  |  |

|           |  |  |  |

|           |  |  |  |

|           |  |  |  |

|           |  |  |  |

|           |  |  |  |

Thank you for helping C&H to deliver the best possible product. Your support is appreciated.

Sincerely,

F. R. Harrison President and CEO

# **INSTRUCTIONS**

In its continuing effort to improve documentation, C&H Technologies, Inc. provides this form for use in submitting any comments or suggestions that the user may have. This form may be detached, folded along the lines indicated, taped along the loose edge (DO NOT STAPLE), and mailed. Please try to be as specific as possible and reference applicable sections of the manual or drawings if appropriate. Also, indicate if you would like an acknowledgment mailed to you stating whether or not your comments were being incorporated.

NOTE: This form may not be used to request copies of documents or to request waivers, deviations, or clarification of specification requirements on current

| <br>(Fold along this line)      |  |

|---------------------------------|--|

|                                 |  |

|                                 |  |

|                                 |  |

|                                 |  |

|                                 |  |

|                                 |  |

|                                 |  |

|                                 |  |

|                                 |  |

|                                 |  |

|                                 |  |

|                                 |  |

| (Fold along this line)          |  |

| ———— (Fold along this line)———— |  |

C&H Technologies, Inc. Technical Publications 445 Round Rock West Drive Round Rock, Texas 78681-5012