USER'S MANUAL

# INTELLIGENT M-MODULE CARRIER

MODEL VX406C

#### COPYRIGHT

C&H Technologies, Inc. (C&H) provides this manual "as is" without warranty of any kind, either expressed or implied, including but not limited to the implied warranties of merchantability and fitness for a particular purpose. C&H may make improvements and/or changes in the product(s) and/or program(s) described in this manual at any time and without notice.

This publication could contain technical inaccuracies or typographical errors. Changes are periodically made to the information herein; these changes will be incorporated in new editions of this publication.

#### Copyright © 2008 by C&H Technologies, Inc.

The information and/or drawings set forth in this document and all rights in and to inventions disclosed herein which might be granted thereon disclosing or employing the materials, methods, techniques, or apparatus described herein, are the exclusive property of C&H Technologies, Inc.

A Reader's Comment Form is provided at the back of this publication. If this form has been removed address comments to:

C&H Technologies, Inc. Technical Publications 445 Round Rock West Drive Austin, Texas 78681-5012

Or visit our web site for support information at:

http://www.chtech.com.

C&H may use or distribute any of the information you supply in any way that it believes appropriate without incurring any obligations.

#### **AMENDMENT NOTICE**

C&H Technologies, Inc. makes every attempt to provide up-to-date manuals with the associated equipment. Occasionally, changes are made to the equipment wherein it is necessary to provide amendments to the manual. If any amendments are provided for this manual they are printed on colored paper and will be provided with the module and manual. Manual updates may also be found on out web site at www.chtech.com.

#### NOTE

The contents of any amendment may affect operation, maintenance, or calibration of the equipment.

### **INTRODUCTION**

This manual describes the operation and use of the C&H Model VX406C Intelligent M-Module Carrier Module (Part Number 11028550). This VXI module is one of a number of test and data acquisition/control modules in the VME and VXI format provided by C&H.

Contained within this manual are the physical and electrical specifications, installation and startup procedures, functional description, and configuration guidelines to adequately use the product.

The part numbers covered by this manual are:

Part NumberDescription11028550-0001VX406C Intelligent M-Module Carrier

# TABLE OF CONTENTS

| 1.0 GEN  | ERAL DES | SCRIPTION                        | 1  |

|----------|----------|----------------------------------|----|

| 1.1      | PURPOSI  | E OF EQUIPMENT                   | 1  |

| 1.2      | SPECIFIC | CATIONS OF EQUIPMENT             | 1  |

|          | 1.2.1    | Key Features                     |    |

|          | 1.2.2    | Specifications                   |    |

|          | 1.2.3    | Electrical                       | 2  |

|          |          | 1.2.3.1 +5V Supply               | 2  |

|          |          | 1.2.3.2± 12V Supply              | 3  |

|          |          | 1.2.3.3 M-Module Power           |    |

|          |          | 1.2.3.4 PMC Power                | 3  |

|          |          | 1.2.3.5 +24V Auxiliary Power     | 3  |

|          |          | 1.2.3.6 +5V Auxiliary Power      |    |

|          | 1.2.4    | Mechanical                       |    |

|          | 1.2.5    | Environmental                    | 4  |

|          | 1.2.6    | Bus Compliance                   | 4  |

| 2.0 INST | ALLATIO  | N                                |    |

| 2.1      | UNPACK   | ING AND INSPECTION               | 5  |

| 2.2      | HANDLI   | NG PRECAUTIONS                   | 5  |

| 2.3      | INSTALL  | ATION OF M-MODULES               | 5  |

| 2.4      | INSTALL  | ATION OF PMC MODULES             | 7  |

| 2.5      | INSTALL  | ATION OF VX406C CARRIER          | 7  |

| 2.6      |          | ATION FOR RESHIPMENT             |    |

| 3.0 FUN  | CTIONAL  | OVERVIEW                         | 9  |

| 3.1      | GENERA   | L                                | 9  |

| 3.2      | HARDWA   | ARE OVERVIEW                     | 9  |

|          | 3.2.1    | M-Modules                        | 10 |

|          | 3.2.2    | Shared Memory                    | 10 |

|          | 3.2.3    | PowerPC and Peripherals          | 11 |

|          | 3.2.4    | VXI Interface Logic              | 11 |

|          | 3.2.5    | PMC Slot                         | 11 |

|          | 3.2.6    | External Drivers                 | 11 |

|          | 3.2.7    | External Input                   | 11 |

|          | 3.2.8    | JTAG/COP Interface               | 12 |

| 3.3      | SOFTWA   | RE OVERVIEW                      | 12 |

| 3.4      | HARDWA   | ARE CONFIGURATION                | 13 |

|          | 3.4.1    | Logical Address Switch           | 14 |

|          | 3.4.2    | Module Configuration Switch      | 14 |

|          | 3.4.3    | PowerPC Configuration Switches   | 16 |

|          | 3.4.4    | VIO Configuration Jumper         | 17 |

| 3.5      | CONNEC   | TORS                             | 18 |

|          | 3.5.1    | External Power Connectors        | 18 |

|          | 3.5.2    | External Relay Drivers Connector | 18 |

|          | 3.5.3    | External Input Connector         | 18 |

|          | 3.5.4    | JTAG/COP Connector               | 18 |

|     |     | 3.5.5         | Serial Co | omm Connector                    | 18 |

|-----|-----|---------------|-----------|----------------------------------|----|

|     |     | 3.5.6         | PMC Co    | nnectors                         | 19 |

|     |     | 3.5.7         | PMC I/O   | Connector                        | 19 |

|     |     | 3.5.8         | VXI Con   | inectors                         | 19 |

|     |     | 3.5.9         | VXI Loc   | al Bus Connector                 | 19 |

|     |     | 3.5.10        |           | le Connectors                    |    |

| 4.0 | SYS |               |           | RE                               |    |

|     | 4.1 |               |           |                                  |    |

|     | 4.2 |               |           | CHITECTURE                       |    |

|     | 1.2 | 4.2.1         |           | C Memory Map                     |    |

|     |     | 4.2.2         |           |                                  |    |

|     |     | 4.2.3         |           | M                                |    |

|     |     | 4.2.4         |           | emory                            |    |

|     |     | 4.2.5         |           | Architecture                     |    |

|     |     | 4.2.3         |           | PCIbus Enumeration               |    |

|     |     |               |           |                                  |    |

|     |     |               |           | IDSEL Signal Routing             |    |

|     |     |               |           | PCI Interrupts                   |    |

|     |     |               |           | Shared Memory Device             |    |

|     |     |               |           | PCI to M-Module Bridge           |    |

|     |     |               |           | PMC Device                       |    |

|     |     | 4.2.6         | 00        | ~ .                              |    |

|     |     | 4.2.7         | -         | ns Registers                     |    |

|     |     | 4.2.8         |           | Drivers                          |    |

|     |     | 4.2.9         |           | TTL Inputs                       |    |

|     |     | 4.2.10        | Watchdo   | g Timer                          | 30 |

|     |     |               |           | OP Interface                     |    |

|     | 4.3 | HOST-SII      | DE ARCH   | ITECTURE                         | 30 |

|     |     | 4.3.1         | VXI Mer   | nory Map                         | 31 |

|     |     | 4.3.2         | Data Bus  | Width                            | 33 |

|     |     | 4.3.3         | PCI Bus   | Mastering and Direct Access      | 33 |

|     | 4.4 | SHARED        | RESOUR    | CES AND DEVICE COMMUNICATIONS    | 33 |

|     |     | 4.4.1         | Operation | ns Registers                     | 34 |

|     |     |               | 4.4.1.1   | VXI Configuration Registers      | 35 |

|     |     |               |           | VXI Communication Registers      |    |

|     |     |               |           | VX406C Carrier Control Registers |    |

|     |     | 4.4.2         |           | rd Serial Protocol               |    |

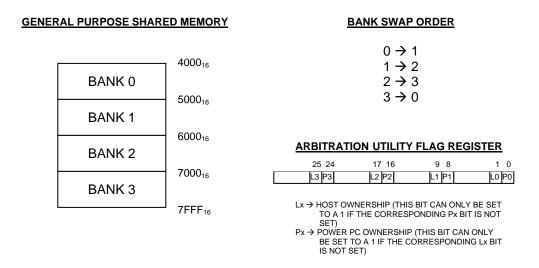

|     |     | 4.4.3         | General I | Purpose Shared Memory            | 44 |

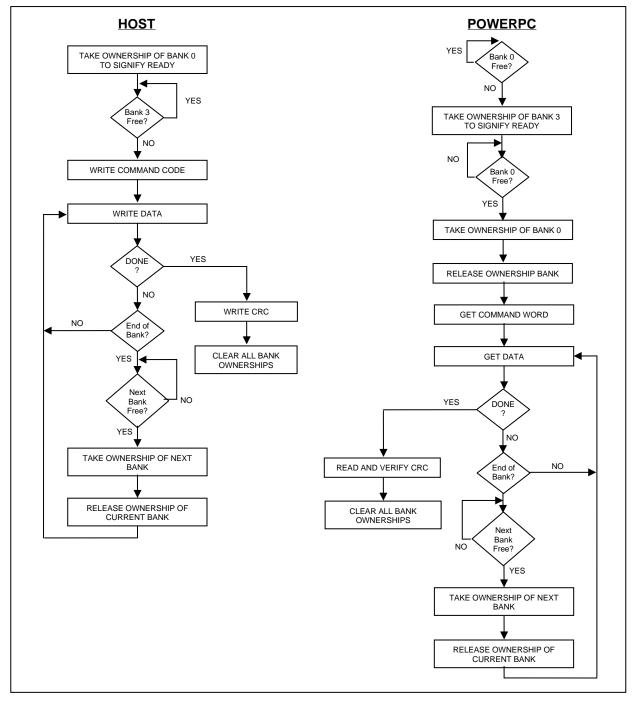

|     |     |               |           | Shared Memory Arbitration        |    |

|     |     |               |           | DMA/Burst                        |    |

|     |     | 4.4.4         |           | age Unit                         |    |

|     |     | 4.4.5         | -         | Purpose FIFOs                    |    |

|     | 4.5 |               |           | HITECTURE                        |    |

|     | 4.6 |               |           | DFTWARE                          |    |

|     | 4.7 |               |           | EM FIRMWARE                      |    |

|     | 1.7 | 4.7.1         |           | le                               |    |

|     |     | <b>T</b> ./.1 |           | PowerPC Initialization           |    |

|     |     |               | 4./.1.1   |                                  |    |

|     |      |           | 4.7.1.2               | Launching the Operating System        |     |

|-----|------|-----------|-----------------------|---------------------------------------|-----|

|     |      |           | 4.7.1.3               | Firmware Download Utility             | 50  |

|     |      | 4.7.2     | ICOS                  |                                       | 50  |

|     |      | 4.7.3     | 3 <sup>rd</sup> Party | RTOS Support                          | 50  |

|     |      | 4.7.4     | User Ap               | plication                             |     |

| 5.0 | PRO  | GRAMMIN   | IG INSTF              | RUCTIONS                              | 53  |

|     | 5.1  | GENERA    | L                     |                                       | 53  |

|     | 5.2  | FLASH P   | ROGRAM                | /MING                                 | 53  |

|     | 5.3  | PCI ACC   | ESSES                 |                                       | 54  |

|     | 5.4  |           |                       | ESS                                   |     |

|     | 5.5  | FIRMWA    | RE UPD                | ATE MODE                              | 55  |

|     |      | 5.5.1     | Firmwar               | e Update Mode Protocol                | 55  |

|     |      |           | 5.5.1.1               | Flash Program Command                 | 58  |

|     |      |           | 5.5.1.2               | Calculating the CRC                   | 58  |

|     | 5.6  | INTERRU   | JPTS                  |                                       | 59  |

|     |      | 5.6.1     | PCI Inte              | rrupts                                | 59  |

|     |      | 5.6.2     | M-Modu                | Ile Interrupts                        | 60  |

|     |      | 5.6.3     | VXI Inte              | errupts                               | 60  |

|     | 5.7  | CONFIGU   | <b>JRING</b> T        | RIGGERS                               | 61  |

|     | 5.8  | HOST-SI   | DE PCI B              | US MASTERING AND DIRECT ACCESS        | 61  |

|     |      |           | 5.8.1.1               | PCI Configuration Accesses            |     |

|     |      |           | 5.8.1.2               | Byte Enables in a Direct Access Cycle | 63  |

|     |      |           |                       |                                       |     |

|     |      |           |                       | S                                     |     |

| API | PEND | IX B CONF | FIGURAT               | ION REGISTERS                         | B-1 |

# LIST OF FIGURES

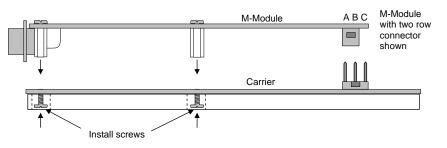

| Figure 1. M-Module Installation                            | 6     |

|------------------------------------------------------------|-------|

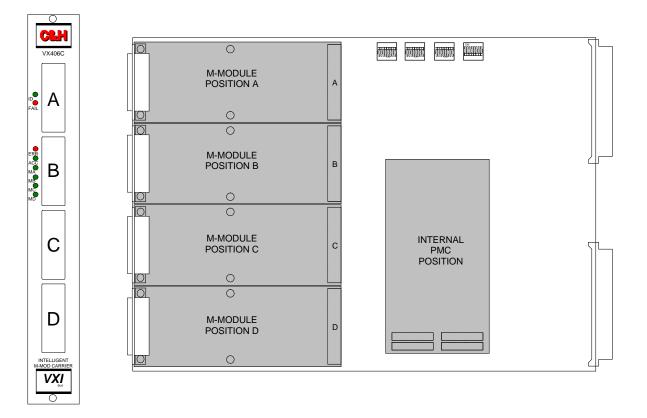

| Figure 2. Front Panel and Top View (Top Shield Not Shown)  | 6     |

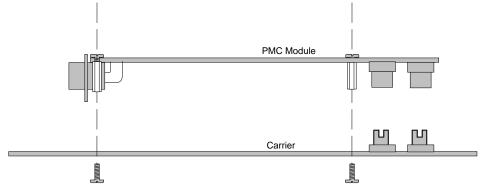

| Figure 3. PMC Module Installation                          | 7     |

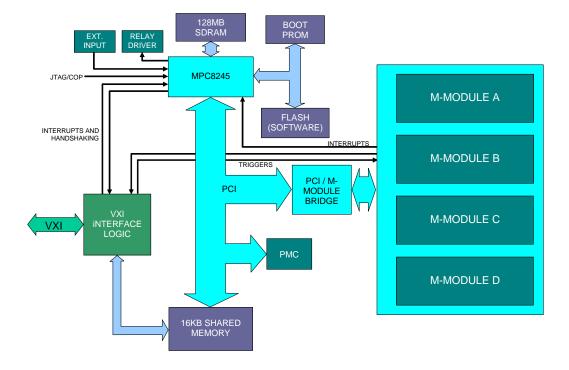

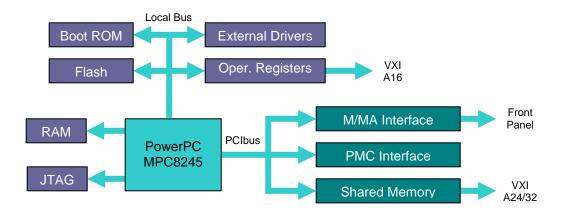

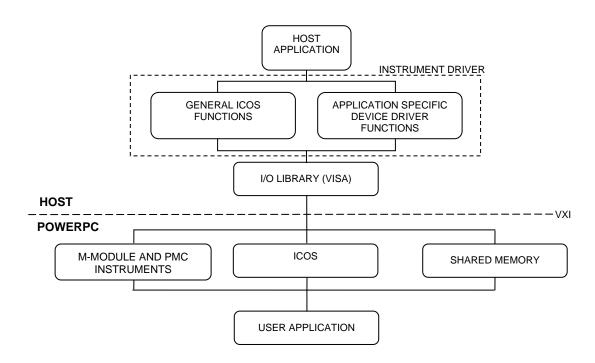

| Figure 4. System Hardware Architecture                     | 10    |

| Figure 5. Hardware Layout                                  |       |

| Figure 6. Logical Address Configuration Switch             | 14    |

| Figure 7. Module Configuration Switch                      | 14    |

| Figure 8. PowerPC Configuration Switches                   | 16    |

| Figure 9. VIO Configuration Jumper                         | 18    |

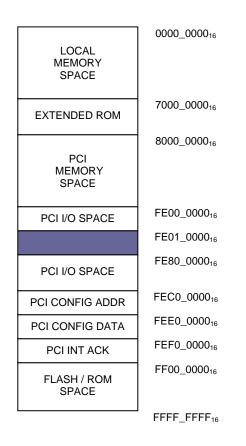

| Figure 10. Device-Side Architecture                        | 21    |

| Figure 11. Address Map Overview                            | 22    |

| Figure 12. Detailed PowerPC Address Map                    | 23    |

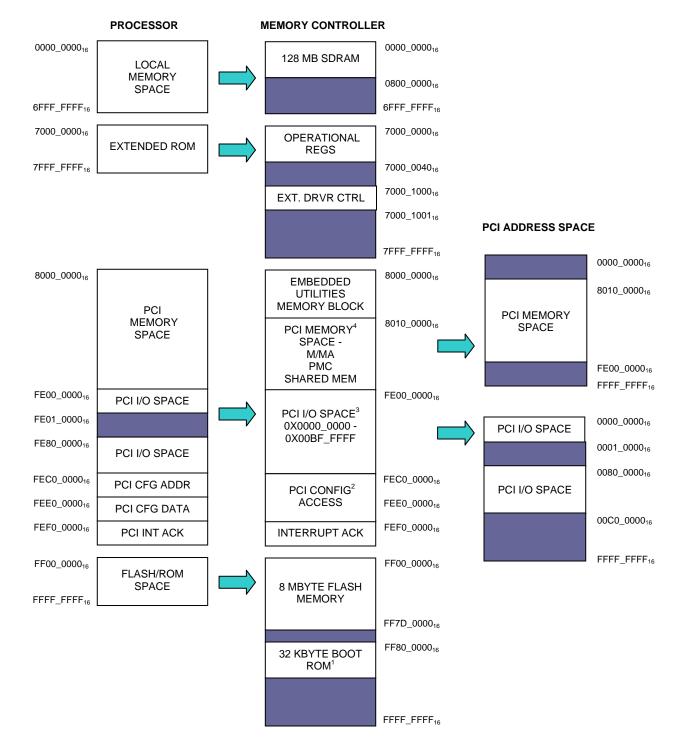

| Figure 13. Shared Memory Organization                      | 26    |

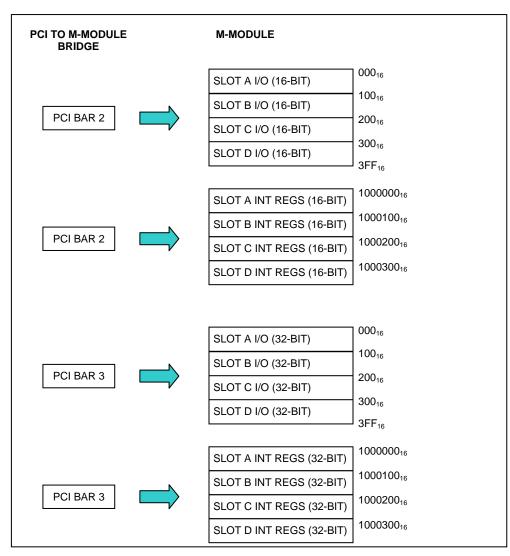

| Figure 14. PCI to M-Module Address Map                     | 27    |

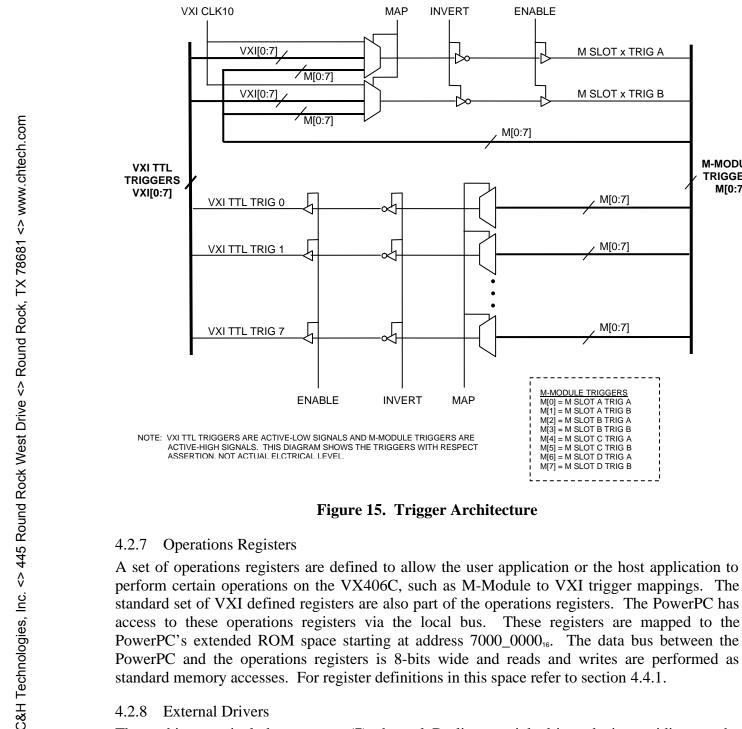

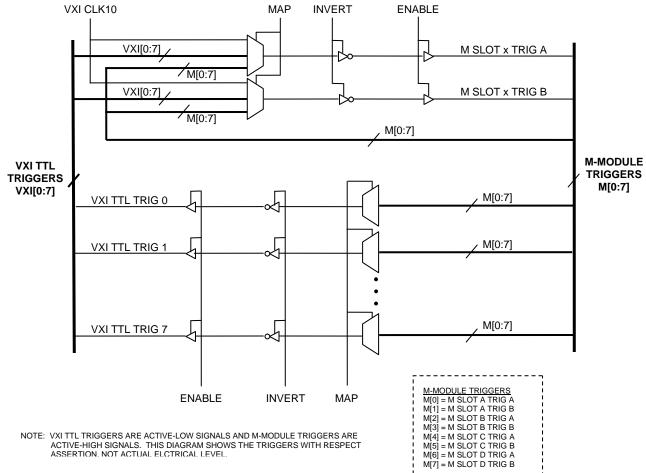

| Figure 15. Trigger Architecture                            | 29    |

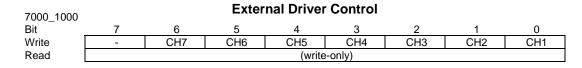

| Figure 16. External Driver Control Register                | 30    |

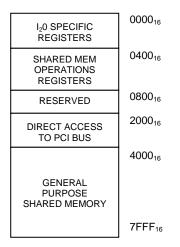

| Figure 17. Host-Side Architecture                          | 31    |

| Figure 18. VXI Memory Organization                         | 32    |

| Figure 19. Shared Resources                                | 34    |

| Figure 20. VXI Configuration Registers                     | 36    |

| Figure 21. VXI Communications Registers                    |       |

| Figure 22. VX406C Control Registers                        | 41    |

| Figure 23. Shared Memory Arbitration Utility Flag Register | 45    |

| Figure 24. General Purpose FIFO Registers                  | 47    |

| Figure 25. System Software Architecture                    |       |

| Figure 26. M-Module Internal Bridge Registers              | 55    |

| Figure 27. Shared memory banks for firmware update         | 56    |

| Figure 28. Firmware Update Protocol                        | 57    |

| Figure 29. Flash Program Command                           |       |

| Figure 30. CRC Calculation - Example Source Code           |       |

| Figure 31. Direct Access Control Register                  | 62    |

|                                                            |       |

| Figure A-1. M-Module Connector Configuration               | . A-1 |

| Figure A-2. VXI P1 Pin Configuration                       |       |

| Figure A-3. VXI P2 Pin Configuration                       |       |

| Figure A-4. PMC Pin Configuration                          |       |

| Figure A-5. PMC Pin Configuration (continued)              |       |

| Figure A-6. External Driver Outputs                        |       |

| Figure A-7. External Inputs                                |       |

| Figure A-8. Serial Comm                                    |       |

| Figure A-9. JTAG/COP Header                                |       |

| Figure A-10. External Power Connectors                     |       |

| Figure A-11. PMC I/O Connector                             | A-7   |

# LIST OF TABLES

| Table I. PowerPC Configuration Signals     |     |

|--------------------------------------------|-----|

| Table II. IDSEL Signal Routing             |     |

| Table III. PCI Interrupt Signal Routing    |     |

| Table IV. Operations Registers Map         |     |

|                                            |     |

| Table B-1. PowerPC Configuration Registers | B-1 |

C&H Technologies, Inc. <> 445 Round Rock West Drive <> Round Rock, TX 78681 <> www.chtech.com

# **1.0 GENERAL DESCRIPTION**

The VX406C is an intelligent VXI carrier module that provides an electrical and mechanical interface for up to four ANSI Standard M-Modules and one PMC module. It features an on-board 32-bit PowerPC<sup>®</sup> processor that can perform command translation, data analysis, and many other data processing or process control functions. For a complete list of M-Modules compatible with the VX406C, visit the SUPPORT $\rightarrow$ M-MODULE SUPPORT DIRECTORY on C&H's website (www.chtech.com).

## 1.1 PURPOSE OF EQUIPMENT

The VX406C was designed for Automated Test Equipment (ATE) applications requiring onboard instrument intelligence or data processing. Some of the more common applications include: legacy instrument emulation, data intensive signal acquisition, high speed signal analysis, and control processing.

## **1.2 SPECIFICATIONS OF EQUIPMENT**

- 1.2.1 Key Features

- 300MHz Freescale MPC8245 Integrated Processor

- Supports up to four ANSI/VITA 12-1996 compliant single-wide M-Modules, or any valid combination of 2, 3, or 4-wide modules.

- Supports extended M-Module functions (MA) such as extended 24-bit addressing, 32bit data bus, and triggers

- Supports one 33 MHz, 5V or 3.3V PMC device

- 128 megabytes SDRAM

- I6 kilobytes dual-ported SRAM accessible by both the processor and VXI

- 8 megabytes flash memory

- VXI A24/A32 access to shared memory

- VXI block transfers to/from shared memory

- DMA transfers between PowerPC, M-Modules, PMC device, and shared memory

- Direct access to M-Modules and PMC module from VXI

- Intelligent Carrier Operating System (ICOS) supports application firmware development

## 1.2.2 Specifications

#### **Processor:**

- Freescale 300MHZ MPC8245

- MPC603e core

- 16KB/16KB L1 Integrated Cache

#### **Local PCI Bus:**

• 33MHZ 32-bit

#### Main Memory:

- 128MB SDRAM

- 8MB Flash, VXI programmable

- 32KB Boot ROM, socketed

#### Shared Memory:

- 16 KB Dual-ported SRAM

- Four 32 deep 32-bit FIFO's

- DMA/Burst support

- Internal arbitration

- Fully accessible by both VXI and PowerPC

#### **M-Module Interface:**

- Up to four ANSI Standard M-Modules

- ANSI/VITA Standard 12-1996

- M-Module triggers map to VXI TTL triggers

- M-Module interrupt to PowerPC

#### **PMC Interface:**

- Support for one PMC module

- IEEE P1386.1 32-bit compliant

- 33MHz 32-bit

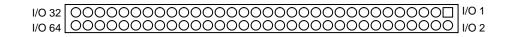

- PMC I/O connected to 64-pin header

#### **External Relay Control:**

- Darlington relay driver, 7-channels, 50V, 350ma

- Use internal +5V supply or external power

#### **External Input:**

- Four TTL inputs

- Allows direct external control of application firmware

#### **Interrupts:**

- M-Module to PowerPC interrupt support

- PowerPC to VXI interrupt level 1-7 (programmable)

- VXI Host to PowerPC interrupt support

#### **Temperature:**

| Operating: | 0°C to 50°C   |

|------------|---------------|

| Storage:   | -40°C to 70°C |

#### **Direct Access:**

- Direct VXI access of M-Modules and PMC

- Up to 8K of local PCI address space can be directly mapped to VXI A24 or A32 space

#### **Debugging Interface:**

- Common On-Chip Processor (COP)/JTAG

- Standard COP header

- Third-party development tools supported

#### C&H Intelligent Carrier Operating System (ICOS):

- Boot-up and initialization

- VXI word serial protocol support

- Firmware download to Flash memory via VXI

- Application Programming Interface

#### **3<sup>rd</sup> Party RTOS Support:**

Architecture supports common real-time operating systems, such as VxWorks, OS-9, Linux, and others.

## 1.2.3 Electrical

The VX406C requires the +5V and  $\pm 12V$  from the VXI backplane. The +5V supply drives a DC to DC converter that supplies +3.3V power to internal on-board devices and to the PMC position. The  $\pm 12V$  power is only used by installed M-Module or PMC modules.

## 1.2.3.1 +5V Supply

The VXI backplane can provide a total of 8.4 amps (1.2A per pin) of +5 volts, of which, the VX406C uses approximately 1.8 amps (9W) for internal purposes. The remaining 6.6 amps (33W) is available to the M-Modules, PMC, and auxiliary power connector through a combination of the +5V and +3.3V supplies. M-Modules do not use +3.3V power, so any power not used by the PMC is available to the M-Modules via the +5V supply. The +5V supply has a replaceable inline 10A fast blow fuse to protect the internal traces of the VX406C.

## 1.2.3.2 ±12V Supply

The  $\pm 12$  volt supplies are not used internally by the carrier; however, may be required by an installed M-Module or PMC module. Each VXI  $\pm 12$  volt supply has an inline replaceable 3A slow-blow fuse to protect the internal traces of the VX406C.

## 1.2.3.3 M-Module Power

Each M-Module position is provided individually fused and filtered +5V, +12V, and -12V power. The +5V supply has an inline 3A power-off resettable fuse and the  $\pm 12V$  supplies have inline 1.25A power-off resettable fuses to protect the internal traces of the VX406C. Note that the M-Module specification limits +5V power consumption to 1A and  $\pm 12V$  power consumption to 200mA per M-Module position. The VX406C allows that specification to be exceeded; however, total power consumption must remain within the available power limits discussed in Section 1.2.3.1. Refer to the documentation provided with an installed M-Module to determine its power requirements.

## 1.2.3.4 PMC Power

The PMC position is provided individually fused and filtered +5V, +3.3V, +12V, and -12V power. The +5V supply has an inline 3A power-off resettable fuse and the  $\pm 12V$  supplies have inline 1.25A power-off resettable fuses to protect the internal traces of the VX406C. +3.3V power is filtered and short-circuit protected by the on-board 10A +3.3V DCDC converter. The DCDC converter has an efficiency of around 90%, which should be taken into account when calculating power consumption. Total power consumption must remain within the available power limits discussed in Section 1.2.3.1. Refer to the documentation provided with an installed PMC module to determine its power requirements.

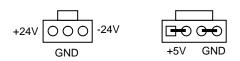

## 1.2.3.5 +24V Auxiliary Power

An auxiliary  $\pm 24V$  power connecter is available for special purpose use. The  $\pm 24V$  supply is not used by the carrier, or the M-Modules and PMC positions. The carrier can supply a maximum of 1 amp (24W) each to the  $\pm 24V$  and the  $\pm 24V$  pins on the connector. Each 24 volt supply has an inline 1A power-off resettable fuse to protect the internal traces of the VX406C.

## 1.2.3.6 +5V Auxiliary Power

An auxiliary +5V power connecter is available for special purpose use. A maximum of 2.5 amps (12.5W) can be provided by the carrier. The connection has an inline 2.5A power-off resettable fuse to protect the internal traces of the VX406C. Any power drawn from this connector reduces the total power available to the M-Module and PMC positions.

## 1.2.4 Mechanical

The mechanical dimensions of the VX406C are in conformance with the VXI bus specification for the height and width of Size-C modules. The nominal dimensions are 233.35 mm (9.187 in) high x 340.0 mm (13.386 in) deep. The module is designed for a standard mainframe with 30.48 mm (1.2 in) width between slots.

## 1.2.5 Environmental

The environmental specifications of the module are:

| Operating Temperature: | $0^{\circ}$ C to $+50^{\circ}$ C |

|------------------------|----------------------------------|

| Storage Temperature:   | -40°C to +70°C                   |

| Humidity:              | <95% without condensation        |

1.2.6 Bus Compliance

The module complies with the VXIbus Specification Revision 1.4 for C-Size VXI modules and with VMEbus Specification ANSI/IEEE STD 1014-1987, IEC 821.

| Manufacturer ID:     | $FC1_{16}$ (can also be set by PowerPC) |

|----------------------|-----------------------------------------|

| Model Code:          | $FDF_{16}$ (can also be set by PowerPC) |

| VXI Access Type:     | Register Based or Message Based         |

| VXI Addressing:      | A16/A24/A32                             |

| VXI Data Transfer:   | D16/D32                                 |

| VXI Sysfail:         | supported                               |

| VXI Interrupts:      | ROAK, programmable levels               |

| VXI Local Bus:       | Available                               |

| TTL Triggers         | SYNC trigger protocol supported         |

| Memory Requirements: | 32 Kilobytes                            |

The module's on-board M-Module bus complies with ANSI/VITA 12-1996 and the following features are supported:

| M-Module Bus Data Width: | D08, D16, D32                 |

|--------------------------|-------------------------------|

| M-Module Address Modes:  | A08                           |

| M-Module Triggers:       | TRIGA, TRIGB (input & output) |

| M-Module Interrupts:     | INTA, INTB, INTC              |

| M-Module Identification: | supported                     |

The modules on-board PMC bus complies with the PMC Specification IEEE P1386.1 for 32-bit PMC modules.

| PMC Bus Data Width: | 32-bit                         |

|---------------------|--------------------------------|

| PMC Bus Speed       | 33 MHz                         |

| PMC Bus Voltage     | 5V or 3.3V (jumper selectable) |

| PMC Rear I/O:       | 64-pin Header                  |

## 2.0 INSTALLATION

## 2.1 UNPACKING AND INSPECTION

In most cases the VX406C is individually sealed and packaged for shipment. Verify that there has been no damage to the shipping container. If damage exists then the container should be retained as it will provide evidence of carrier caused problems. Such problems should be reported to the carrier immediately as well as to C&H. If there is no damage to the shipping container, carefully remove the module from its box and anti static bag and inspect for any signs of physical damage. If damage exists, report immediately to C&H.

# 2.2 HANDLING PRECAUTIONS

The VX406C contains components that are sensitive to electrostatic discharge. When handling the module for any reason, do so at a static-controlled workstation, whenever possible. At a minimum, avoid work areas that are potential static sources, such as carpeted areas. Avoid unnecessary contact with the components on the module.

## 2.3 INSTALLATION OF M-MODULES

M-Modules must be installed before the VX406C is installed into the VXI system. To install M-Modules, remove the VX406C's top shield and front panel covers as needed. *There is never a need to remove the VX406C's bottom shield*. Install an M-Module by firmly pressing the connector on the M-Module together with the connector on the carrier as shown in Figure 1. Secure the M-Module through the holes on the bottom shield using screws provided with the M-Module.

CAUTION: The VX406C supports M-Modules that use either two or three row interface connectors. Extra caution must be taken for M-Modules that use two row connectors to ensure they are correctly positioned to use rows A and B on the carrier. When using M-Modules with two row connectors, row C on the VX406C is left unconnected.

CAUTION: M-Module connectors are NOT keyed. Use extra caution to avoid misalignment. Applying power to a misaligned module can damage the M-Module and carrier.

Figure 1. M-Module Installation

There are four possible mounting locations on the carrier: A, B, C, and D. M-Modules may be installed into any of the four locations. The mounting locations are illustrated in Figure 2.

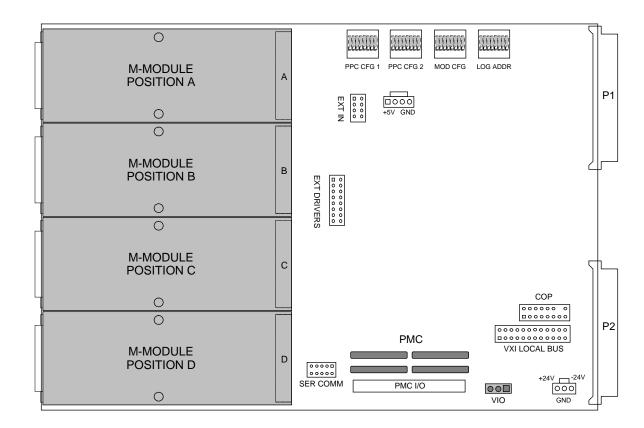

Figure 2. Front Panel and Top View (Top Shield Not Shown)

#### 2.4 INSTALLATION OF PMC MODULES

A PMC module must be installed into the carrier before the carrier is installed into the host system. To install a PMC module, remove the VX406C's top shield. *There is never a need to remove the VX406C's bottom shield*. Firmly press the connector on the PMC module together with the connector on the carrier as shown in Figure 3. Secure the module through the holes in the bottom shield using the screws provided with the PMC module.

Figure 3. PMC Module Installation

### 2.5 INSTALLATION OF VX406C CARRIER

If necessary, remove the top shield from the VX406C and configure the switches and jumpers. Set the module's logical address and addressing mode as described in section 3.4. Replace the shield and insert the carrier into the appropriate slot according to the desired priority and apply power. If no obvious problems exist, proceed to communicate with the module as outlined throughout the rest of this manual.

CAUTION: Read the entire User's Manual before proceeding with the installation and application of power.

#### 2.6 PREPARATION FOR RESHIPMENT

If the module is to be shipped separately it should be enclosed in a suitable water and vapor proof anti static bag. Heat seal or tape the bag to insure a moisture-proof closure. When sealing the bag, keep trapped air volume to a minimum.

The shipping container should be a rigid box of sufficient size and strength to protect the equipment from damage. If the module was received separately from a C&H system, then the original module shipping container and packing material may be re-used if it is still in good condition.

C&H Technologies, Inc. <> 445 Round Rock West Drive <> Round Rock, TX 78681 <> www.chtech.com

#### **3.0 FUNCTIONAL OVERVIEW**

#### **3.1 GENERAL**

The VX406C provides an intelligent interface between the VXI bus and up to four M-Modules and one PMC module. It features an embedded processor system powered by a MPC8245 PowerPC integrated processor. An on-board PCI bus provides an interface to the four M-Modules, the PMC module position, and 16 kilobytes of shared memory. VXI interface logic provides an interface between the VXI bus and the PowerPC via the shared memory and the PowerPC's local bus.

C&H Intelligent Carrier Operating System (ICOS) is provided to assist an embedded user application in performing necessary tasks or to allow the carrier to function normally when no user application is used. ICOS utilities include: boot-up and initialization routines, system configuration routines, VXI communications routines, an application programming interface (API), and various hardware interface routines to provide a basic interface to the carrier and installed modules and to assist application development. Refer to the Intelligent Carrier Operating System User's Manual (C&H Document No. 11028578) for details on ICOS.

For more advanced application development, a Linux distribution and Linux embedded development kit is also available from C&H for the VX406C. The Linux distribution includes all the items needed to create an embedded Linux system including a bootloader, patched kernel, root filesystem and many standard utilities. In addition, the processor architecture supports various other 3<sup>rd</sup> party commercially available real time operating systems.

#### 3.2 HARDWARE OVERVIEW

The VX406C is powered by a highly integrated MPC8245 microprocessor with a PowerPC 603e core, a built-in Peripheral Component Interconnect (PCI) interface, and an advanced memory controller. The processor along with flash memory, ROM memory, and SDRAM form a complete embedded processing system with all the peripherals necessary for flexible application development.

Dual-ported shared memory and VXI interface logic allow for seamless communication between the VXI host and the PowerPC. Interrupts and handshaking logic is also provided to assist communications between the host and PowerPC.

A single PMC positions and four M-Module positions residing on the on-board PCI bus allow a variety of instruments and peripherals to be added to the system. Both the VXI host and the PowerPC can communicate with and control the modules.

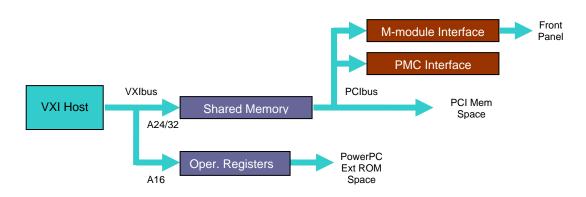

Finally, relay driver logic and external TTL input logic allow special control hardware to be easily added to the overall integrated system. Figure 4 illustrates the system hardware architecture.

Figure 4. System Hardware Architecture

### 3.2.1 M-Modules

The M-Modules provide the measurement and control functionality for the given application. The carrier can support up to four single-wide M-Modules or any valid combination of 2, 3, or 4-wide modules. The modules interface to the on-board PCI bus through a PCI to M-Module Interface Bridge. Both the PowerPC application and the VXI host can communicate with and control the modules. A variety of M-Modules are commercially available from numerous manufacturers. For a complete list of M-Modules compatible with the VX406C, visit the SUPPORT $\rightarrow$ M-MODULE SUPPORT DIRECTORY on C&H's website (www.chtech.com).

## 3.2.2 Shared Memory

The 16 kilobyte shared memory device acts as a buffer between the VXI bus and the on-board PCI bus. The device provides 16 kilobytes of dual-port SRAM and various other communications utilities such as general purpose FIFO's. It connects to the VXI bus through a local bus interface controlled by the VXI interface logic and to the PowerPC through the PCI bus. The device performs on-chip memory arbitration allowing the 16 kilobytes of memory to be accessed at the same time from both the VXI bus and the PowerPC. It also contains an embedded PCI bus controller allowing the VXI bus to directly access the on-board PCI bus and thus directly access the M-Modules and the PMC module.

## 3.2.3 PowerPC and Peripherals

The PowerPC architecture was designed as a standard embedded processor system. It consists of a MPC8245 PowerPC, a boot ROM device, 128 megabytes of P133 SDRAM, and a flash memory device. This architecture allows the developer to select from standard off-the-shelf development tools and real-time operating systems for application development.

The PowerPC acts as the PCI bus master and can access the M-Modules, the PMC module, and the shared memory device. It also can access the VXI interface logic to perform handshaking between itself and the VXI bus.

# 3.2.4 VXI Interface Logic

The VXI interface logic acts as a transparent interface between the VXI bus and the shared memory device. It translates VXI bus accesses into shared memory local bus accesses by managing all local bus address and control lines. It maps all of the shared memory device's address space to VXI A24/A32 space.

The VXI interface also handles handshaking between the PowerPC and the VXI bus. It includes a set of registers that are mapped to VXI A16 space and are accessible by the PowerPC to handle host to device communications and handshaking.

Finally the interface logic provides VXI bus trigger and interrupt capabilities. The carrier has extensive mapping capabilities between the M-Module trigger lines and the VXI bus trigger lines controllable by the VXI host. In addition, VXI interrupts can be generated by the PowerPC application on any of the 8 VXI interrupt levels.

# 3.2.5 PMC Slot

The PMC slot on the PCI bus can be used to add additional functionality to the application. For example, a mass storage device could be added for on-board data collection by installing a PMC disk drive controller. It is also common to host a PMC Ethernet controller for embedded development pruposes. The PMC position is accessible by both the PowerPC and the VXI host.

# 3.2.6 External Drivers

The PowerPC can control a Darlington sink driver device residing on its local memory bus. The device's outputs are available at a 16 pin header for external use. The device is intended to drive external relays, display LED's, or other high current devices.

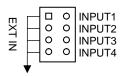

# 3.2.7 External Input

Four external TTL input lines can be read by the PowerPC. The signals are available at an external connector on the carrier. These lines allow direct external control of the application software.

# 3.2.8 JTAG/COP Interface

The JTAG interface to the PowerPC provides a debug and development interface supported by many standard off-the-shelf developments tools. The interface is used by development tools to communicate with the processor. It provides the developer with the ability to view system registers, view memory, set breakpoints, and use other standard debugging practices.

# 3.3 SOFTWARE OVERVIEW

The embedded software on the carrier as well as the host software are very application dependant and thus, must be developed specifically to suit the needs of the particular application. However, firmware is provided as part of the Intelligent Carrier Operating System (ICOS) to assist application development and to provide basic functionality when no user application exists. In addition a Linux distribution is available from C&H.

The Intelligent Carrier Operating System (ICOS) is a single-threaded OS kernel specifically designed for use on the VX406C and C&H Technologies' other intelligent carriers. When no user application exists, ICOS provides basic functionality allowing the user to communicate with the carrier and the M-Modules and PMC module. A limited set of VXI message based commands are available as well as the ability to access all defined registers and the shared memory. In this capacity, the carrier can operate as a fully functional instrument without the existence of a user application.

If a user application is to be provided, ICOS assists the developer in performing several tasks that require advanced knowledge of the carrier architecture and the devices that make up that architecture. For example a system routine is provided to program the flash memory so that the developer does not need to refer to the flash device's data sheet to learn the programming protocol. Also, ICOS automatically handles the communications required for VXI message passing so that the application can concentrate on performing high level tasks and not on the details of the VXI word serial protocol. ICOS is completely independent and fully interrupt and exception driven so that it only takes up a very small amount of processor resources and so the user application can be independently compiled and linked without knowledge of ICOS memory organization.

An ICOS User's Manual (C&H Document No. 11028578) is available from C&H Technologies detailing the operating system environment.

The Linux distribution available from C&H includes the DAS U-boot bootloader, a customized Linux kernel and a custom root filesystem that contains many familiar Linux utilities. Application development is performed using common open source development and debug tools and the C&H Linux Embedded Development includes the necessary hardware and software to ease application development. Contact C&H Technologies for details on the available Linux distribution and the Linux Embedded Development Kit.

The VX406C architecture also supports various 3<sup>rd</sup> party Real-Time Operating Systems (RTOS). Full support of 3<sup>rd</sup> party operating systems will depend on the availability of various VX406C specific software components for the RTOS. Contact the RTOS vendor and C&H Technologies for information on support for a particular RTOS.

## 3.4 HARDWARE CONFIGURATION

There are several switch and jumper selectable settings that configure the VX406C for operation. Configuration options include: the VXI logical address, PowerPC options, programming modes, and operational voltages. Figure 5 shows the layout of all the switches and jumpers on the VX406C.

Figure 5. Hardware Layout

## 3.4.1 Logical Address Switch

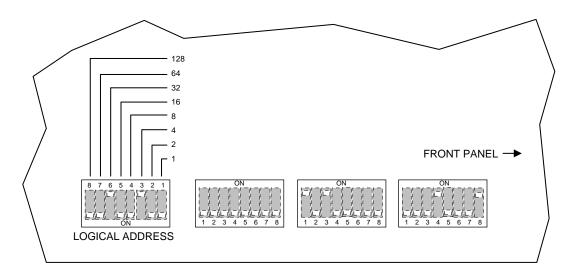

The logical address switch determines the logical address for the VX406C. The switch forms a binary weighted decimal value that sets the logical address of the module. The OFF position for each switch represents a binary one in that bit position. For example, the switch settings shown in Figure 6 would result in a logical address of 36.

Figure 6. Logical Address Configuration Switch

# 3.4.2 Module Configuration Switch

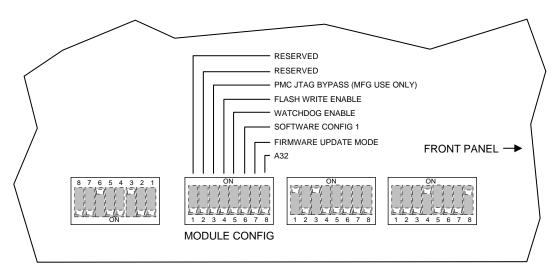

The module configuration switch is used to set some of the miscellaneous options on the VX406C. Figure 7 shows the options that are configurable with this switch.

Figure 7. Module Configuration Switch

<u>PMC JTAG Bypass Switch (Manufacturing Use Only)</u>: This switch will bypass the PMC device's JTAG interface by automatically daisy chaining the JTAG input to the JTAG output at the PMC connector. The JTAG bus is daisy chained between the PMC connector and other devices on the carrier. It is necessary to bypass the PMC position when using the JTAG interface to program the other devices during manufacturing. The user should never have to bypass the PMC JTAG interface and should therefore leave this switch in the OFF position. *The PowerPC's JTAG/COP interface is an independent JTAG interface and is not affected by this switch*.

<u>Flash Write Enable Switch</u>: This switch will enable or disable the ability for software to program flash memory. Setting this switch to ON will enable the flash programming capability. When the switch is OFF the carrier will not allow the PowerPC to program the flash device.

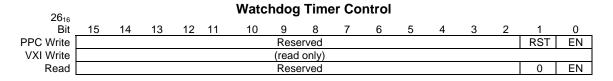

<u>Watchdog Enable Switch</u>: The Watchdog Enable Switch enables/disables the watchdog timer at the hardware level. The watchdog timer may also be disabled by software by writing to the Watchdog Timer Control Register (Offset 0x26). *Disabling the watchdog timer at the hardware level is required to utilize a JTAG debugger on the processor.*

<u>Software Configuration Switch</u>: The software configuration switch is available for use by the user application and system firmware. This switch has no effect on the hardware operation of the VX406C. The value of the switch is copied to the operations registers so that the software can read the value and define the switch's function. Setting the switch to ON results in the corresponding bit of the operations register being set to a binary '0'. OFF corresponds to a binary '1'.

ICOS or other system software may use this switch for a specific purpose. Refer to the ICOS User's Manual or the manual of your system software for details.

<u>Firmware Update Mode Switch</u>: This switch determines whether the VX406C boots normally or into a mode where the system firmware can be updated. If this switch is set to OFF at power-up, the carrier will go into the firmware update mode and wait for firmware to be downloaded via the VXI bus. If this switch is ON at power-up, the carrier will initialize normally and launch the system firmware or operating system.

<u>A32 Switch</u>: This switch selects whether the VX406C performs VXI A24 or A32 address decoding. This address space is used to access the shared memory device. If this switch is set to ON, the carrier requests memory in the systems A32 address space, otherwise A24 address space is requested.

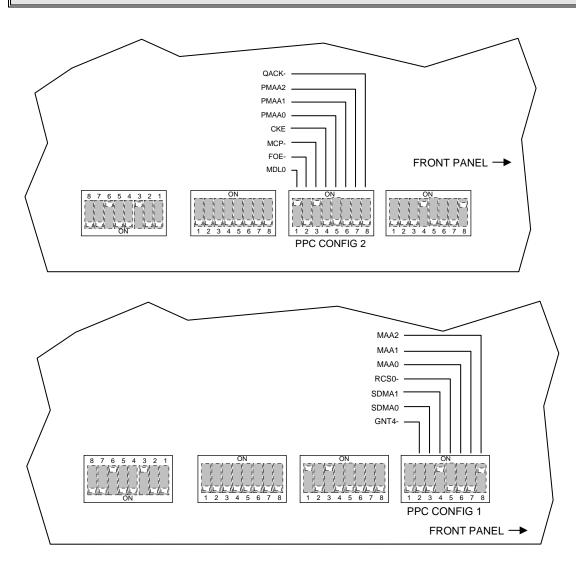

# 3.4.3 PowerPC Configuration Switches

The PowerPC configuration switches determine the value of various signals during reset. Each signal connected to these switches is a reset configuration signal for the PowerPC. The values of these signals at reset, determine the configuration of the processor. Figure 8 shows all available PowerPC reset configuration signals. Table I briefly describes each option and all possible settings. For details on reset configuration refer to the MPC8245 User's Manual.

WARNING: The PowerPC configuration switches are preset during manufacturing to the optimal settings for the VX406C. Modifying these settings is rarely necessary and in some cases may cause the VX406C to not function correctly.

Figure 8. PowerPC Configuration Switches

| Signal          | Description                                                                                                                                                | Settings                                                                                                                                                                                                                                                                                                                                                                               |

|-----------------|------------------------------------------------------------------------------------------------------------------------------------------------------------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| MDL0,<br>FOE-   | Selects the data bus width for ROM bank 0 and SDRAM                                                                                                        | (MDL0 = 0, FOE_ = 0) = ROM 32-bit, SDRAM 32-bit<br>(MDL0 = 0, FOE_ = 1) = ROM 8-bit, SDRAM 32-bit <sup>1,2</sup><br>(MDL0 = 1, FOE_ = 0) = ROM 64-bit, SDRAM 64-bit<br>(MDL0 = 1, FOE_ = 1) = ROM 8-bit, SDRAM 64-bit                                                                                                                                                                  |

| MCP-,<br>CKE    | Sets the PCI output hold delay value<br>(in nanoseconds) relative to<br>PCI_SYNC_IN. Refer to the<br>MPC8245 documentation for details<br>on each setting. | $(MCP_{-} = 0, CKE = 0)$ $(MCP_{-} = 0, CKE = 1)$ $(MCP_{-} = 0, CKE = 1)$ $(MCP_{-} = 1, CKE = 0)$ $(MCP_{-} = 1, CKE = 1)$ |

| PMAA0,<br>PMAA1 | Memory signal driver capabilities.                                                                                                                         | (PMAA0 = 0, PMAA1 = 0) = reserved<br>(PMAA0 = 0, PMAA1 = 1) = 40 $\Omega$ drive capability<br>(PMAA0 = 1, PMAA1 = 0) = 20 $\Omega$ drive capability<br>(PMAA0 = 1, PMAA1 = 1) = 6 $\Omega$ drive capability <sup>1,3</sup>                                                                                                                                                             |

| PMAA2           | PCI and EPIC controller driver capabilities                                                                                                                | <b>0</b> = 40 $\Omega$ drive capability <sup>1,2,3</sup><br>1 = 20 $\Omega$ drive capability (except for IRQ2/S_RST and<br>IRQ3/S_FRAME- signals which have 6 $\Omega$ drive<br>capability)                                                                                                                                                                                            |

| QACK-           | Clock Flip Disable                                                                                                                                         | 0 = Clock flip enabled<br>1 = No clock flip <sup>1,2</sup>                                                                                                                                                                                                                                                                                                                             |

| GNT4-           | Debug Address Disable                                                                                                                                      | 0 = Debug address enabled<br><b>1 = Debug address disabled</b> <sup>1,2</sup>                                                                                                                                                                                                                                                                                                          |

| SDMA0           | DUART Signals Disabled                                                                                                                                     | 0 = DUART signals enabled<br>1 = PCI_CLK[0:3] signal used instead of DUART <sup>1,2</sup>                                                                                                                                                                                                                                                                                              |

| SDMA1           | Extended Addressing Mode                                                                                                                                   | <b>0</b> = Extended addressing mode enabled <sup>1,2</sup><br>1 = Extended addressing mode disabled                                                                                                                                                                                                                                                                                    |

| RCS0-           | Boot Memory Location                                                                                                                                       | 0 = Boot ROM is located on the PCI bus<br>1 = Boot ROM is located on the local bus <sup>1,2</sup>                                                                                                                                                                                                                                                                                      |

| MAA0            | Address Map Setting. The<br>MPC8245 only supports address<br>map B.                                                                                        | 0 = Invalid<br><b>1 = MPC8245</b> is configured for address map <b>B</b> <sup>1,2</sup>                                                                                                                                                                                                                                                                                                |

| MAA1            | PCI Host Mode                                                                                                                                              | 0 = MPC8245 is a PCI agent device<br>1 = MPC8245 is a PCI master device <sup>1,2</sup>                                                                                                                                                                                                                                                                                                 |

| MAA2            | PCI Arbiter Disable                                                                                                                                        | <b>0</b> = <b>PCI</b> arbiter enabled <sup>1,2</sup><br>1 = PCI arbiter disabled                                                                                                                                                                                                                                                                                                       |

| Table I.  | <b>PowerPC</b> | Configuration | Signals |

|-----------|----------------|---------------|---------|

| I able I. |                | Comiguiation  | Dignais |

Notes: 1. Bold indicates the recommended setting for the VX406C 2. 1=Switch OFF, 0=Switch ON (except for PMAA2 see note 3)

3. For the PMAA2 switch, 1=Switch ON, 0=Switch OFF

## 3.4.4 VIO Configuration Jumper

The VIO configuration jumper selects the voltage level supplied to the VIO pin on the PCI bus and PMC connector. The VIO power signal is used by universal PMC modules that can operate in both +5V and +3.3V systems. On these boards, the power for the I/O buffers is provided by the VIO pin instead of directly from the +3.3V or +5V power pins. Set the jumper according to the PMC module installed on the carrier as shown in Figure 9.

The other devices on the PCI bus (i.e. shared memory and M-Module bridge) can operate at either 3.3V or 5V signaling therefore, if no PMC module is installed, either jumper position is acceptable. The jumper must be installed for the PCI bus to operate.

Figure 9. VIO Configuration Jumper

# **3.5 CONNECTORS**

The VX406C incorporates several connectors to provide a physical connection to its various interfaces. Figure 5 shows the general location of each connector on the VX406C. Detailed pinout information can be found in Appendix A. A short description of each connector is provided in the following sections.

# 3.5.1 External Power Connectors

Two connectors are provided to connect +5V, +24V and -24V externally. The +5V connection is provided at a Molex 70543 male 4-pin connector. The +24V and -24V connections are provided by a Molex 70543 male 3-pin connector. Refer to Appendix A for details on the connector pin-outs.

# 3.5.2 External Relay Drivers Connector

The external relay driver's output signals are available at a 16-pin header (8x2 with 0.100 inch centers). Refer to Appendix A for details on the header pin-outs. Relay power can be externally supplied by removing jumper between +5V and COMMON and connecting power to COMMON pins. If internally +5V power is used (jumper installed), be sure to observe current specifications.

# 3.5.3 External Input Connector

The four external TTL input lines are available at a standard 8-pin female header (4x2 with 0.100 inch centers). Refer to Appendix A for details on the header pin-outs.

# 3.5.4 JTAG/COP Connector

Connection to the PowerPC's JTAG/COP debug interface is provided through a keyed 16-pin header (8x2 with 0.100 inch centers). This header is the standard size and employs the standard pin-out used by most JTAG based emulators. The pin-out details of the JTAG/COP header can be found in Appendix A.

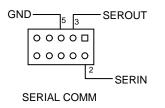

# 3.5.5 Serial Comm Connector

Serial communication to the PowerPC is available at a standard 10-pin female header (5x2 with 0.100 inch centers). Refer to Appendix A for details on the header pin-outs.

### 3.5.6 PMC Connectors

The four PMC connectors provide the physical interface to a PMC module. The connectors are configured in accordance with the PMC specification. Refer to Appendix A for pin-out details.

#### 3.5.7 PMC I/O Connector

Some PMC modules provide 64 bits of I/O to the PMC carrier board though the PMC rear connectors. On the VX406C these 64 bits of I/O are available at the PMC I/O connector. The connector is a standard 64-pin header (32x2 with 0.100 inch centers). Refer to Appendix A for pin-out details.

#### 3.5.8 VXI Connectors

The rear connectors, labeled P1 and P2, provide the physical interface to the VXI system. They are configured in accordance with the VXI specification. Refer to Appendix A for pin-out details.

## 3.5.9 VXI Local Bus Connector

The VXI Local Bus signals are available at a standard 24-pin header (12x2 with 0.100 inch centers). The VX406C does not use the VXI Local Bus internally but makes it available for external use at this connector.

#### 3.5.10 M-Module Connectors

The four M-Module connectors provide the physical interface for up to four ANSI Standard M-Modules. The connectors are configured in accordance with the M-Module specification. Refer to Appendix A for pin-out details.

C&H Technologies, Inc. <> 445 Round Rock West Drive <> Round Rock, TX 78681 <> www.chtech.com

## **4.0 SYSTEM ARCHITECTURE**

#### 4.1 OVERVIEW

The system architecture illustrated in Figure 4 is viewed differently from an application running on the embedded PowerPC than from an application running on the VXI host. Most of the carrier's hardware can be accessed by both applications but, the methods for doing so differ. The system architecture is best described by viewing the host-side and the device-side separately. However, it is also important to understand how the resources shared between both applications are used for host to device communications.

## **4.2 DEVICE-SIDE ARCHITECTURE**

The device-side architecture is anchored by a standard embedded processor system powered by the MPC8245 PowerPC. The architecture provides on-board RAM, boot ROM, and flash memory to support the software application. The PowerPC acts as the PCI bus master and has full access to all devices on the PCI bus. A set of operational registers, the external relay driver and the external TTL inputs are available to the application via the processor's local bus. Figure 10 illustrates the device-side architecture.

Figure 10. Device-Side Architecture

#### 4.2.1 PowerPC Memory Map

Being a 32-bit processor, the MPC8245 can address up to 4 Gigabytes of physical memory. On the VX406C, the processor maps this 4 Gigabytes of memory into a configuration designated as Address Map B. The address map B configuration divides the memory space into sections that, when accessed, translate the operation to a local memory, PCI memory, PCI I/O, or ROM access. Figure 11 shows the general layout of address map B.

Figure 11. Address Map Overview

Details of the address map B implementation for the VX406C architecture are shown in Figure 12. Each section in the address map directly addresses a resource in the system architecture. Further details of each address block are provided throughout this document. Other address map B options and settings are also available but generally not used on the VX406C. Refer to the MPC8245 User's Manual for details.

Notes:

- 1. The boot ROM device only decodes 15 address lines. Therefore, the boot ROM is repeated throughout the address space. For example, address FF80\_0000<sub>16</sub> is the same location as FFF0\_000<sub>16</sub>. Addresses FEC0\_0000<sub>16</sub> and FEE0\_0000<sub>16</sub> are used to perform PCI configuration accesses as described in section 5.3.

- 2.

- PCI I/O accesses are forwarded to the PCI bus with the 8 most significant bits of the address cleared. 3.

- (i.e. processor address FE80\_0000<sub>16</sub> = PCI I/O address 0080\_0000<sub>16</sub>)

M-module addresses are mapped to the PCI memory space via the PCI to M-module Bridge. Refer to section 4.2.5.5 for details.

#### Figure 12. Detailed PowerPC Address Map

# 4.2.2 SDRAM

The SDRAM provides 128 Megabytes of temporary storage for the application. The memory is organized in a 13 rows x 10 columns x 4 banks configuration. It has a 10ns access time and a 32 bits wide data bus. It is accessed through the PowerPC's addresses space starting at offset 0.

## 4.2.3 Boot ROM

The boot ROM provides 64 kilobytes of non-volatile, read-only memory. It is normally programmed during the manufacturing process to contain boot code and initialization routines. It can not be reprogrammed in circuit. The boot ROM is mapped to PowerPC address FF80\_0000<sub>16</sub> and has an 8-bit data bus. Only 15 address bits are decoded so that the 64 kilobytes are repeated throughout the PowerPC's ROM/Flash space between addresses FF80\_0000<sub>16</sub> and FFFF\_FFFF<sub>16</sub>. Consequently, the default exception vector table starting at address FFF0\_0000h resides in the boot ROM device.

# 4.2.4 Flash Memory

The flash device provides 8 megabytes of non-volatile storage for code and data. Unlike the boot ROM, flash is programmable in circuit and may be used by the system firmware. The flash device is accessed starting at PowerPC address FF00\_0000<sub>16</sub> and has an 8-bit wide data bus. Reads from flash are performed as standard PowerPC memory accesses. Programming and erasing the device, however, requires a sequence of commands to be sent to the device. C&H ICOS provides commands for programming the flash device. For details on using ICOS to program flash, refer to the C&H ICOS User's Manual. In addition, a hardware configuration switch is available to enable/disable programming of the flash device. If disabled, firmware can neither write-to nor erase the device.

# 4.2.5 PCIbus Architecture

The on-board PCI bus can contain up to 4 devices including the PowerPC which acts as the bus master. If a PCI to PCI Bridge is added at the PMC interface, more devices are available and can be accessed by the PowerPC. The devices on the primary bus include the PowerPC, the shared memory device, a PMC device, and the PCI to M-Module bridge. The bus operates at 33 MHz and 5V or 3.3V (jumper selectable).

PCI memory, configuration, and I/O space is memory mapped directly into the PowerPC's address map as shown in Figure 12. Approximately 2 gigabytes of PCI memory space is mapped starting at address 8010\_0000<sub>16</sub>. Each device requiring memory will have a base address within this mapped area. About 4 megabytes of PCI I/O space is mapped to PowerPC addresses FE00\_0000<sub>16</sub>. When performing a PCI I/O access, the processor clears the upper 8 bits of the address before forwarding the transaction to the PCI bus. So, for example, accessing processor address FE80\_0000<sub>16</sub> will read or write PCI I/O address 0080\_0000<sub>16</sub>. The base address of each device is determined by the PCI enumeration routines during initialization. The base address of a particular device can be determined by reading its Base Address Register (BAR) register in PCI configuration space for that device.

To perform a single PCI configuration write or read, two processor accesses are required. First, the PCI configuration address register at PowerPC address  $FEC0_0000_{16}$  must be set to point to the correct device and offset. Then the data can be read from or written to the PCI configuration

data register at PowerPC address FEE0\_0000<sub>16</sub>. The PCI configuration address register value is determined by the bus number, IDSEL signal routing, device function number, and the register offset. For details on performing PCI configuration accesses refer to the MPC8245 User's Manual. ICOS routines are provided that an application can use to easily perform configuration reads and writes. For details on ICOS refer to the ICOS User's Manual.

## 4.2.5.1 PCIbus Enumeration

During initialization, the boot-up firmware will search the PCI bus for devices, determine the resources needed for each device, and allocate processor resources accordingly. This procedure determines where in the PowerPC memory map a particular PCI device's resources are located. PCI device mapping is not guaranteed from one carrier configuration to another or even from one firmware version to another. The application software should always check a device's configuration registers for resource mapping information prior to accessing the device.

# 4.2.5.2 IDSEL Signal Routing

Each device on the PCI bus has a unique ID select line used to specify the destination of a configuration access. The PCI specification does not stipulate the source of each ID select line; however, the upper 16-bits of the address bus are normally used. On the VX406C each device has its IDSEL line tied to a specific address line as shown in Table II. The device number, normally provided to software routines, is also system dependant. Table II also shows the device numbering used on the VX406C. This information must be incorporated into a configuration access by the application when performing a write or read.

| Device                 | IDSEL | DevNum           |

|------------------------|-------|------------------|

| Shared Memory          | AD16  | 1610             |

| PowerPC                | AD17  | 17 <sub>10</sub> |

| • PMC                  | AD18  | 1810             |

| PCI to M-Module Bridge | AD19  | 19 <sub>10</sub> |

Table II. IDSEL Signal Routing

# 4.2.5.3 PCI Interrupts

The PowerPC's Embedded Programmable Interrupt Controller (EPIC) acts as the PCI interrupt controller. The interrupt lines from the PCI devices and M-Modules are routed to the EPIC controller's five interrupt inputs as shown in Table III. The PCI to M-Module bridge device does not generate interrupts. Instead each M-Module's interrupt line is routed directly to the EPIC controller. This architecture requires that the PMC interface and the shared memory device share a common interrupt line. It is up to the application software to determine the source of an interrupt on this shared line. The C&H ICOS firmware contains routines to assist the application developer in handling interrupts. Refer to the C&H ICOS User's Manual and the MPC8245 User's Manual for information on programming the EPIC controller to handle interrupts.

| Device        | PCI Interrupt Pin   | EPIC IRQ |

|---------------|---------------------|----------|

| M-Module A    | N/A                 | IRQ0     |

| M-Module B    | N/A                 | IRQ1     |

| M-Module C    | N/A                 | IRQ2     |

| M-Module D    | N/A                 | IRQ3     |

|               |                     |          |

| РМС           | INT A# B#, C#, & D# | IRQ4     |

| Shared Memory | INTA#               | IRQ4     |

**Table III. PCI Interrupt Signal Routing**

#### 4.2.5.4 Shared Memory Device

The shared memory device's entire address space is mapped to PCI memory space including all registers, the  $I_2O$  messaging unit, and the general purpose shared memory. The offset into PowerPC memory space is determined at boot up by the PCI enumeration software.

Figure 13 shows the shared memory device's address map. All addresses are offsets from the devices base address. To determine the shared memory's base address, read offset  $10_{16}$  (BAR0 Register) of the shared memory's PCI configuration space. This value is the base address of the shared memory device. The general purpose shared memory begins at an offset of  $4000_{16}$  from this address. Full details of the shared memory device's address map, including register details, can be found in the *CY7C09449PV Data Sheet* from Cypress Semiconductor, Inc.

Figure 13. Shared Memory Organization

#### 4.2.5.5 PCI to M-Module Bridge

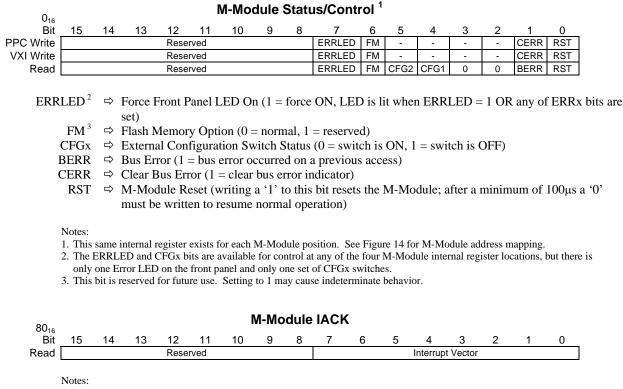

The PCI to M-Module Bridge provides the interface between the on-board PCI bus and the four M-Module positions. All four M-Modules share a common device number and PCI configuration space provided by the bridge. The bridge maps each M-Module's I/O and internal register spaces to PCI memory space as shown in Figure 14. The bridge will automatically translate any access to these PCI locations to the corresponding M-Module access. One of the internal registers provides the ability to perform an interrupt acknowledge cycle on the corresponding M-Module and return the interrupt vector (if supported by the M-Module).

Figure 14. PCI to M-Module Address Map

## 4.2.5.6 PMC Device

The PMC position resides on the on-board PCI bus. Its address space is mapped directly to the PowerPC's address map. The bus mode signals are implemented to inform the PMC module of the PCI bus configuration. The PMC module may contain a PCI to PCI Bridge whose secondary bus is fully accessible by the PowerPC. Interrupts from the PMC device are supported as described in section 4.2.5.3.

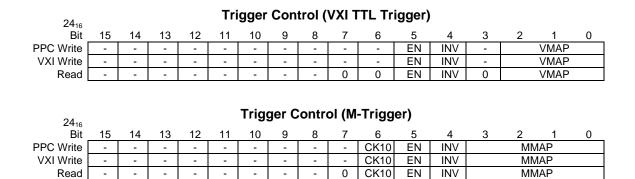

# 4.2.6 Triggers

The carrier includes a programmable switching matrix for mapping M-Module triggers to VXI triggers, other M-Module triggers, or the VXI CLK10 signal. The matrix is illustrated in Figure 15. Each trigger line in the architecture has an output driver that can be enabled or disabled. The source of each driver can be selected from the other trigger lines in the architecture. In effect, a VXI TTL trigger line can be driven by any of the M-Module trigger lines and an M-Module trigger line can be driven by any of the VXI TTL Trigger lines. In addition, the carrier allows for an M-Module trigger line to be driven by another M-Module trigger line or by the VXI CLK10 signal. The architecture also allows for the selected source to be inverted prior to reaching the output driver.

This architecture provides enormous flexibility allowing a large number of trigger-mapping combinations. When programming, care must be taken not to enable an output driver on a trigger line that is already being used for an input. This will not damage the carrier but will prohibit normal functionality of that trigger line. Programming of the matrix is provided via the operations registers discussed in section 4.2.7 and detailed in section 4.4.1.

#### 4.2.8 External Drivers

The architecture includes a seven (7) channel Darlington sink driver device residing on the PowerPC's local memory bus. The device is intended to drive external relays, display LED's, or other devices with high current requirements. The device's outputs are available at a 16 pin header for external use. Refer to section 3.5.2 and Appendix A for details on the header.

PowerPC and the operations registers is 8-bits wide and reads and writes are performed as

standard memory accesses. For register definitions in this space refer to section 4.4.1.

**Figure 15. Trigger Architecture**

Access to the device is provided at address 7000\_1000<sub>16</sub>. The data bus width to the device is 8bits wide and each bit corresponds to one of the 8 channels. The device can only be written to. Figure 16 shows the external driver control register.

CHx  $\Rightarrow$  Channel value (1 = driven, 0 = not driven)

# Figure 16. External Driver Control Register

#### 4.2.9 External TTL Inputs

The PowerPC has access to four general purpose TTL inputs. The inputs can be driven externally at a standard 8-pin header. Refer to section 3.5.3 and APPENDIX A for details on the header. The values of the inputs are stored in the operations registers and can be read by the PowerPC. Refer to section 4.4.1 for details on the operations registers.

# 4.2.10 Watchdog Timer

A watchdog timer is available to reset the processor in the event that an errant software flow occurs. The watchdog can be disabled using the Module Configuration switch described in section 3.4.2 or by software by writing to the Watchdog Timer Control Register (Offset 0x26). *Disabling the watchdog timer at the hardware level is required to utilize a JTAG debugger on the processor.*

# 4.2.11 JTAG/COP Interface

The JTAG interface to the PowerPC provides support for several standard off-the-shelf developments tools. Most development environments for the PowerPC support JTAG based communications with the processor. It provides the developer with the ability to view system registers, view memory, set breakpoints, and use other standard debugging practices. *To utilize a JTAG debugger on the processor, the watchdog timer must be disabled using the Module Configuration switch described in 3.4.2.*

Connection to the JTAG/COP interface is provided through a standard 16 pin header. Refer to section 3.5.4 and Appendix A for details on the header.

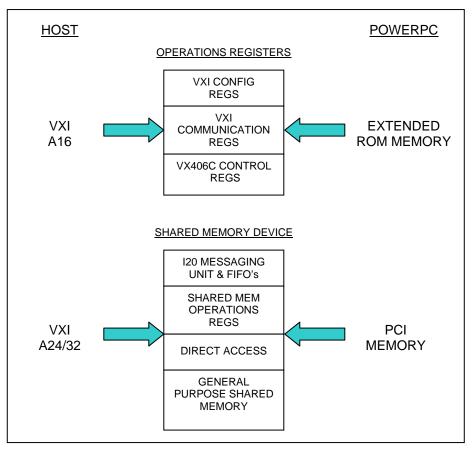

# 4.3 HOST-SIDE ARCHITECTURE

The host-side architecture is anchored by the VXI system including a VXI chassis and a host computer. Standard off-the-shelf VXI controllers from several different manufacturers are available to interface the carrier to the host computer, including high performance embedded controllers. The VXI host has access to the entire address space of the shared memory device as well as to a set of the operations registers. The shared memory device provides a utility to

directly access devices on the PCI bus from the VXI host. Therefore, the VXI host application can control on-board PCI devices and thus the M-Modules without the assistance of the PowerPC. The standard VXI registers required by the VXI specification are implemented as part of the operations registers. These include the registers required to implement the VXI word serial protocol. The VXI host has the ability to fully access all devices on the on-board PCI bus and to fully utilize all host-to-device communications utilities. Figure 17 illustrates the intelligent carrier architecture as viewed from the VXI host computer.

Figure 17. Host-Side Architecture

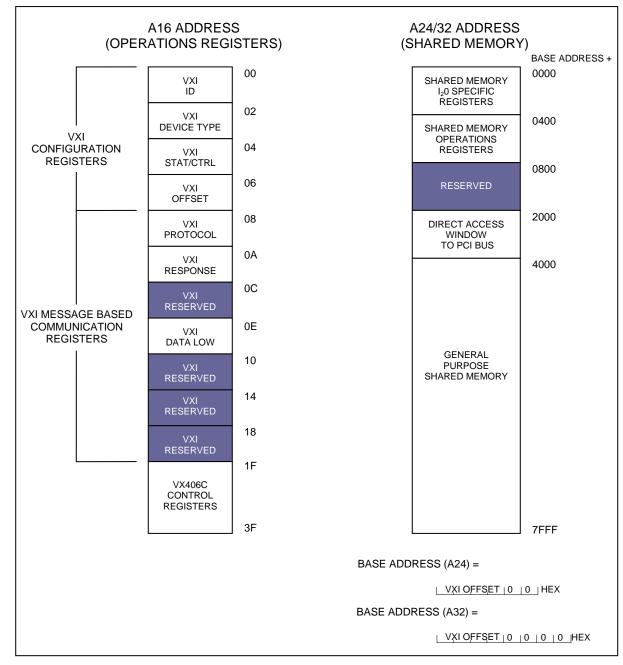

#### 4.3.1 VXI Memory Map

Figure 18 shows the host-side memory organization for the intelligent carrier. The operations registers are accessed via VXI A16 space. These registers include the VXI required registers and the VXI message based communication registers as defined by the VXI bus specification.

A24/A32 memory space is a direct mapping of the shared memory device's memory map. This architecture gives the host full access to the shared memory and its registers including direct access to the PCI bus and other miscellaneous communications utilities.

A24 or A32 addressing is switch selectable as described in section 3.4.2. The VXI resource manager will write a base address to the offset register at address  $06_{16}$  in A16 space. If the carrier is configured for A32 addressing, the carrier will use the value of the offset register as the upper 16 bits of its 32-bit base address. If A24 addressing is selected, the carrier will use the value in the offset register as the upper 16 bits of its 24-bit base address. This behavior is illustrated at the bottom of Figure 18.

Figure 18. VXI Memory Organization

## 4.3.2 Data Bus Width

The intelligent carrier supports 16 and 32-bit wide data transactions to the shared memory device in the A24/A32 address space. However the device must be configured by software to be either 16 or 32-bits, but not both. Differences in the byte lane assignments between the VXI bus and the shared memory's local bus make dynamically switching between D16 and D32 impossible. If both D16 and D32 accesses are required then software must swap the bus width configuration before each type of access.

C&H ICOS provides a system command to configure the data bus width to the shared memory device. Refer to the C&H ICOS User's Manual for details.

Only 16-bit accesses to A16 address space are supported.

# 4.3.3 PCI Bus Mastering and Direct Access

The shared memory device provides an 8 Kilobyte window directly into PCI memory space. This window is accessible by the VXI host at offset  $2000_{16}$  in A24/A32 space. This window gives the host PC direct access to any PCI device residing on the on-board PCI bus including the M-Modules. To point the 8 Kilobyte window to the correct PCI bus address, the host must control the direct access control register defined by the shared memory device. The register is part of the shared memory operation registers accessible by the VXI host in A24/A32 space. Refer to section 5.8 for details on using the direct access capabilities of the carrier.

# 4.4 SHARED RESOURCES AND DEVICE COMMUNICATIONS

Communication between the host-side application and the device-side application is accomplished using a couple of resources available to both the host and the device. Namely, these shared resources are the operations registers and the shared memory device as shown in Figure 19. These shared resources are used to perform VXI communications, device configurations, block data transfers, and other miscellaneous functions.

**Figure 19. Shared Resources**

# 4.4.1 Operations Registers

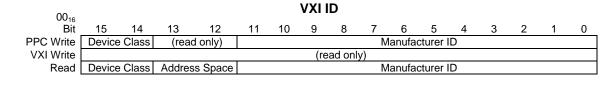

The operations registers combine the required VXI configuration registers, VXI communication registers and a set of carrier control registers. Table IV lists all available registers along with their offset. The VXI host can access each registers at its specified offset in the A16 address space. The PowerPC can access each register at its specified offset in its extended ROM space starting at address  $7000_{-}0000_{16}$ . There may be access restrictions on individual registers or individual bits within a register depending on the whether it is being accessed by the host-side or the device-side application. Refer to the register descriptions in Figure 20, Figure 21, and Figure 22 for details on each register.

NOTE: The PowerPC's interface to the operations registers is only 8-bits wide. In Figure 20, Figure 21, and Figure 22, the least significant bits reside in the low PowerPC address. For example, VXI ID bits 0-7 reside at PowerPC address 0x7000\_0000<sub>16</sub> and bits 8-15 reside at address 0x7000\_0001<sub>16</sub>.

| Offset (Hex) | Register Description      |

|--------------|---------------------------|

| VXI          | Configuration Registers   |

| 00           | VXI ID                    |

| 02           | VXI Device Type           |

| 04           | VXI Status/Control        |

| 06           | VXI Offset Register       |

| VXI C        | Communication Registers   |

| 08           | VXI Protocol              |

| 0A           | VXI Response              |

| 0C           | Reserved                  |

| 0E           | VXI Data Low              |

| 10 - 1F      | Reserved                  |

| VX406C       | Carrier Control Registers |

| 20           | Carrier Status/Control    |

| 22           | VXI Interrupt Control     |

| 24           | Trigger Control           |

| 26           | Watchdog Timer Control    |

| 28-3F        | Reserved                  |

Table IV. Operations Registers Map

### 4.4.1.1 VXI Configuration Registers

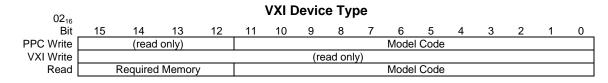

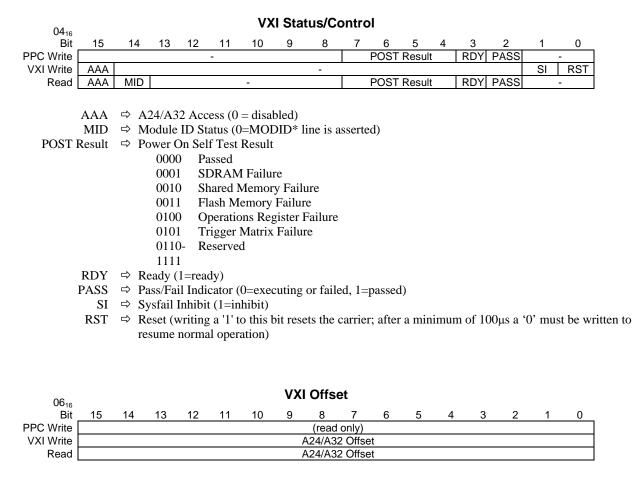

The VXI configuration registers contain basic information needed to configure a VXI system as required by the VXIbus specification. The configuration information includes: manufacturer identification, product model code, device type, memory requirements, device status, and device control. The registers are briefly described below and are detailed in Figure 20.

<u>VXI Identification (ID) Register</u>  $(00_{16})$ : This register provides the manufacturer identification, device classification (i.e., register based or message based), and the addressing mode (i.e. A32 or A24). It is a read only register from the VXI host. The PowerPC can write this register however it should be done immediately after reset prior to running VXI resource manager.